UNISONIC TECHNOLOGIES CO., LTD

# CD4541

# **PROGRAMMABLE TIMER**

## DESCRIPTION

The **CD4541** programmable timer comprise a 16-stage binary counter, an integrated oscillator for use with an external capacitor and two resistors, output control logic, and a special power-on reset circuit. The counter divides the oscillator frequency by any of 4 digitally controlled division ratios.

# FEATURES

- \* Operates at 2<sup>n</sup> frequency divider or as single transition timer

- \* Increments on positive edge clock transitions

- \* Wide supply voltage range: 3.0V ~ 15V

- \* Built-in low power RC oscillator

- \* Oscillator frequency range ~ DC to 100 kHz

- \* External clock applied to Pin 3 can be used instead of

- \* oscillator

- \* Available division ratios 28, 210, 213, or 216

- \* High noise immunity: 0.45 V<sub>DD</sub> (typ.)

- \* Master reset totally independent of automatic reset operation

- \* Automatic reset initializes all counters when power turns on

- \*  $Q/\overline{Q}$  select provides output logic level flexibility

- \* High output drive min. one TTL load

- \* Maximum input leakage 1µA at 15V over full temperature

- \* range

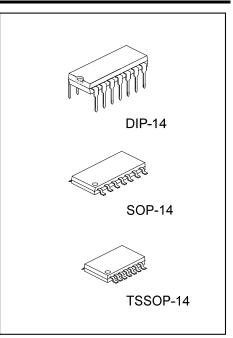

### ORDERING INFORMATION

| Ordering Number |               | Deskara  | Decking   |  |

|-----------------|---------------|----------|-----------|--|

| Lead Free       | Halogen Free  | Package  | Packing   |  |

| CD4541L-D14-T   | CD4541G-D14-T | DIP-14   | Tube      |  |

| CD4541L-S14-R   | CD4541G-S14-R | SOP-14   | Tape Reel |  |

| CD4541L-P14-R   | CD4541G-P14-R | TSSOP-14 | Tape Reel |  |

#### MARKING

| DIP-14                                                                                                       | SOP-14 / TSSOP-14                                                                     |  |  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| 14 12 11 10 9 8 Date Code   UTC □□□□□ L: Lead Free   CD4541 → G: Halogen Free   □□□ Lot Code   1 2 3 4 5 6 7 | 14 13 12 11 10 9 8   UTC □□□□□ L: Lead Free   CD4051□ G: Halogen Free   1 2 3 4 5 6 7 |  |  |

# CD4541

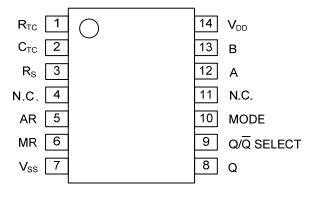

# ■ PIN CONFIGURATION

# TRUTH TABLE

| PIN | STATE                            |                                   |  |  |  |

|-----|----------------------------------|-----------------------------------|--|--|--|

|     | 0                                | 1                                 |  |  |  |

| 5   | Auto Reset Operating             | Auto Reset Disabled               |  |  |  |

| 6   | Timer Operational                | Master Reset On                   |  |  |  |

| 9   | Output Initially Low after Reset | Output Initially High after Reset |  |  |  |

| 10  | Single Cycle Mode                | Recycle Mode                      |  |  |  |

## DIVISION RATIO TABLE

| А | В | Number of Counter Stages<br>n | Count<br>2 <sup>n</sup> |

|---|---|-------------------------------|-------------------------|

| 0 | 0 | 13                            | 8192                    |

| 0 | 1 | 10                            | 1024                    |

| 1 | 0 | 8                             | 256                     |

| 1 | 1 | 16                            | 65536                   |

# ■ ABSOLUTE MAXIMUM RATING

| PARAMETER            |                    | SYMBOL           | RATINGS                     | UNIT |

|----------------------|--------------------|------------------|-----------------------------|------|

| Supply Voltage       |                    | V <sub>DD</sub>  | -0.5 ~ +18                  | V    |

| Input Voltage        |                    | V <sub>IN</sub>  | -0.5 ~ V <sub>DD</sub> +0.5 | V    |

|                      | DIP-14             |                  | 700                         | mW   |

| Power Dissipation    | SOP-14<br>TSSOP-14 | P <sub>D</sub>   | 500                         | mW   |

| Junction Temperature |                    | TJ               | +150                        | °C   |

| Storage Temperature  |                    | T <sub>STG</sub> | -40 ~ +150                  | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

#### RECOMMENDED OPERATING CONDITIONS

| PARAMETER             | SYMBOL          | RATINGS             | UNIT |

|-----------------------|-----------------|---------------------|------|

| Supply Voltage        | V <sub>DD</sub> | 3 ~ 15              | V    |

| Input Voltage         | Vin             | 0 ~ V <sub>DD</sub> | V    |

| Operating Temperature | TA              | -40 ~ +125          | °C   |

#### DC ELECTRICAL CHARACTERISTICS (Unless otherwise specified)

| PARAMETER                        | SYMBOL          | TEST CONDITIONS                                                           | MIN   | TYP               | MAX  | UNIT |

|----------------------------------|-----------------|---------------------------------------------------------------------------|-------|-------------------|------|------|

|                                  |                 | V <sub>DD</sub> = 5V, V <sub>IN</sub> =V <sub>DD</sub> or V <sub>SS</sub> |       | 0.005             | 20   | μA   |

| Quiescent Device Current         | IDD             | V <sub>DD</sub> =10V, V <sub>IN</sub> =V <sub>DD</sub> or V <sub>SS</sub> |       | 0.010             | 40   | μA   |

|                                  |                 | V <sub>DD</sub> =15V, V <sub>IN</sub> =V <sub>DD</sub> or V <sub>SS</sub> |       | 0.015             | 80   | μA   |

|                                  |                 | V <sub>DD</sub> =5V                                                       |       | 0                 | 0.05 | V    |

| Low Level Output Voltage         | Vol             | V <sub>DD</sub> =10V, I I <sub>O</sub> I<1µA                              |       | 0                 | 0.05 | V    |

|                                  |                 | V <sub>DD</sub> =15V                                                      |       | 0                 | 0.05 | V    |

|                                  |                 | V <sub>DD</sub> =5V                                                       | 4.95  | 5                 |      | V    |

| High Level Output Voltage        | Vон             | V <sub>DD</sub> =10V, I I <sub>O</sub> I<1µA                              | 9.95  | 10                |      | V    |

|                                  |                 | V <sub>DD</sub> =15V                                                      | 14.95 | 15                |      | V    |

|                                  | VIL             | $V_{DD}$ =5V, $V_{O}$ =0.5V or 4.5V                                       |       | 2                 | 1.5  | V    |

| Low Level Input Voltage          |                 | V <sub>DD</sub> =10V, V <sub>O</sub> =1.0V or 9.0V                        |       | 4                 | 3.0  | V    |

|                                  |                 | V <sub>DD</sub> =15V, V <sub>O</sub> =1.5V or 13.5V                       |       | 6                 | 4.0  | V    |

|                                  |                 | V <sub>DD</sub> =5V, V <sub>O</sub> =0.5V or 4.5V                         | 3.5   | 3                 |      | V    |

| High Level Input Voltage         | VIH             | V <sub>DD</sub> =10V, V <sub>O</sub> =1.0V or 9.0V                        | 7.0   | 6                 |      | V    |

|                                  |                 | V <sub>DD</sub> =15V, V <sub>O</sub> =1.5V or 13.5V                       | 11.0  | 9                 |      | V    |

|                                  | I <sub>OL</sub> | $V_{DD}$ =5V, $V_{O}$ =0.4V                                               | 1.96  | 3.6               |      | mA   |

| Low Level Output Current (Note)  |                 | V <sub>DD</sub> =10V, V <sub>O</sub> =0.5V                                | 2.66  | 9.0               |      | mA   |

|                                  |                 | V <sub>DD</sub> =15V, V <sub>O</sub> =1.5V                                | 10.4  | 34.0              |      | mA   |

|                                  | I <sub>OH</sub> | V <sub>DD</sub> =5V, V <sub>O</sub> =2.5V                                 | 4.27  | 130               |      | mA   |

| High Level Output Current (Note) |                 | V <sub>DD</sub> =10V, V <sub>O</sub> =9.5V                                | 2.25  | 8.0               |      | mA   |

|                                  |                 | V <sub>DD</sub> =15V, V <sub>O</sub> =13.5V                               | 8.8   | 30.0              |      | mA   |

| la suit Currant                  | I <sub>IN</sub> | V <sub>DD</sub> =15V, V <sub>IN</sub> =0V                                 |       | -10 <sup>-5</sup> | -0.3 | μA   |

| Input Current                    |                 | V <sub>DD</sub> =15V, V <sub>IN</sub> =15V                                |       | 10 <sup>-5</sup>  | 0.3  | μA   |

Note:  $I_{OH}$  and  $I_{OL}$  are tested one output at a time.

| PARAMETER                                                                   | SYMBOL                              | TEST CONDITIONS      | MIN | TYP | MAX | UNIT |

|-----------------------------------------------------------------------------|-------------------------------------|----------------------|-----|-----|-----|------|

| Output Rise Time                                                            | t <sub>тLH</sub>                    | V <sub>DD</sub> =5V  |     | 50  | 200 | ns   |

|                                                                             |                                     | V <sub>DD</sub> =10V |     | 30  | 100 | ns   |

|                                                                             |                                     | V <sub>DD</sub> =15V |     | 25  | 80  | ns   |

|                                                                             |                                     | V <sub>DD</sub> =5V  |     | 50  | 200 | ns   |

| Output Fall Time                                                            | $t_{THL}$                           | V <sub>DD</sub> =10V |     | 30  | 100 | ns   |

|                                                                             |                                     | V <sub>DD</sub> =15V |     | 25  | 80  | ns   |

| Turn Off Turn On Dropogation                                                |                                     | V <sub>DD</sub> =5V  |     | 1.8 | 4.0 | μs   |

| Turn-Off, Turn-On Propagation<br>Delay, Clock to Q (2 <sup>8</sup> Output)  | t <sub>PLH</sub> , t <sub>PHL</sub> | V <sub>DD</sub> =10V |     | 0.6 | 1.5 | μs   |

|                                                                             |                                     | V <sub>DD</sub> =15V |     | 0.4 | 1.0 | μs   |

|                                                                             | t <sub>PHL</sub> , t <sub>PLH</sub> | V <sub>DD</sub> =5V  |     | 3.2 | 8.0 | μs   |

| Turn-On, Turn-Off Propagation<br>Delay, Clock to Q (2 <sup>16</sup> Output) |                                     | V <sub>DD</sub> =10V |     | 1.5 | 3.0 | μs   |

|                                                                             |                                     | V <sub>DD</sub> =15V |     | 1.0 | 2.0 | μs   |

|                                                                             | twh(cl)                             | V <sub>DD</sub> =5V  | 400 | 200 |     | ns   |

| Clock Pulse Width                                                           |                                     | V <sub>DD</sub> =10V | 200 | 100 |     | ns   |

|                                                                             |                                     | V <sub>DD</sub> =15V | 150 | 70  |     | ns   |

|                                                                             | f <sub>CL</sub>                     | V <sub>DD</sub> =5V  |     | 2.5 | 1.0 | MHz  |

| Clock Pulse Frequency                                                       |                                     | V <sub>DD</sub> =10V |     | 6.0 | 3.0 | MHz  |

|                                                                             |                                     | V <sub>DD</sub> =15V |     | 8.5 | 4.0 | MHz  |

|                                                                             | twh(R)                              | V <sub>DD</sub> =5V  | 400 | 170 |     | ns   |

| MR Pulse Width                                                              |                                     | V <sub>DD</sub> =10V | 200 | 75  |     | ns   |

|                                                                             |                                     | V <sub>DD</sub> =15V | 150 | 50  |     | ns   |

| Average Input Capacitance                                                   | Ci                                  | Any Input            |     | 5.0 | 7.5 | pF   |

| Power Dissipation Capacitance                                               | CPD                                 | (Note 2)             |     | 100 |     | pF   |

#### ■ AC ELECTRICAL CHARACTERISTICS (CL=50pF (refer to test circuits) (Note 1)

Notes: 1. AC Parameters are guaranteed by DC correlated testing.

2.  $C_{\text{PD}}$  determines the no load AC power consumption of any CMOS device.

#### OPERATING CHARACTERISTICS

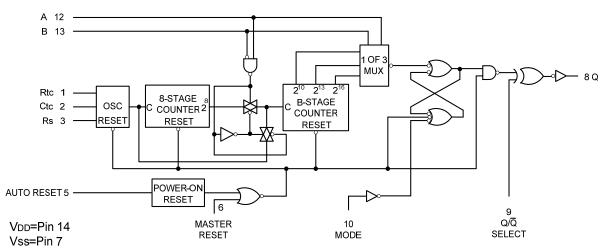

With Auto Reset pin set to a "0" the counter circuit is initialized by turning on power. Or with power already on, the counter circuit is reset when the Master Reset pin is set to a "1". Both types of reset will result in synchronously resetting all counter stages independent of counter state.

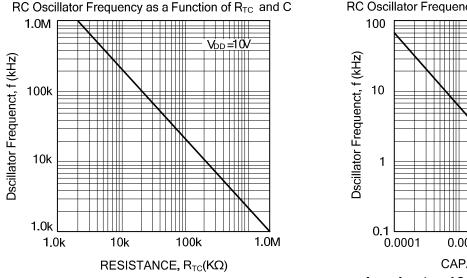

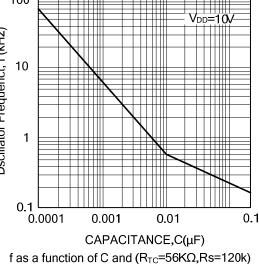

The RC oscillator frequency is determined by the external RC network, i.e.:

$$f=\frac{1}{2.3 R_{TC}C_{TC}}$$

if (1 kHz  $\leq f \leq 100$  kHz)

and RS ~ 2  $R_{TC}$  where RS  $\geq \! 10 \; k\Omega$

The time select inputs (A and B) provide a two-bit address to output any one of four counter stages (2<sup>8</sup>, 2<sup>10</sup>, 2<sup>13</sup>, and 2<sup>16</sup>). The 2<sup>n</sup> counts as shown in the Division Ratio Table represent the Q output of the Nth stage of the counter. When A is "1", 2<sup>16</sup> is selected for both states of B.

However, when B is "0", normal counting is interrupted and the 9th counter stage receives its clock directly from the oscillator (i.e., effectively outputting  $2^8$ ).

The  $Q/\overline{Q}$  select output control pin provides for a choice of output level. When the counter is in a reset condition and Q/Q select pin is set to a "0" the Q output is a "0". Correspondingly, when  $Q/\overline{Q}$  select pin is set to a "1" the Q output is a "1".

When the mode control pin is set to a "1", the selected count is continually transmitted to the output. But, with mode pin "0" and after a reset condition the RS flip-flop resets (see Logic Diagram), counting commences and after  $2^{n-1}$  counts the RS flip-flop sets which causes the output to change state. Hence, after another  $2^{n-1}$  counts the output will not change. Thus, a Master Reset pulse must be applied or a change in the mode pin level is required to reset the single cycle operation.

f as a function of  $R_{TC}$  and (C=100pF, Rs=2 $R_{TC}$ )

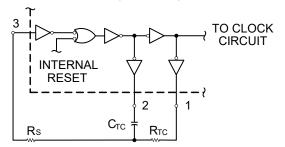

Oscillator Circuit Using RC Configuration

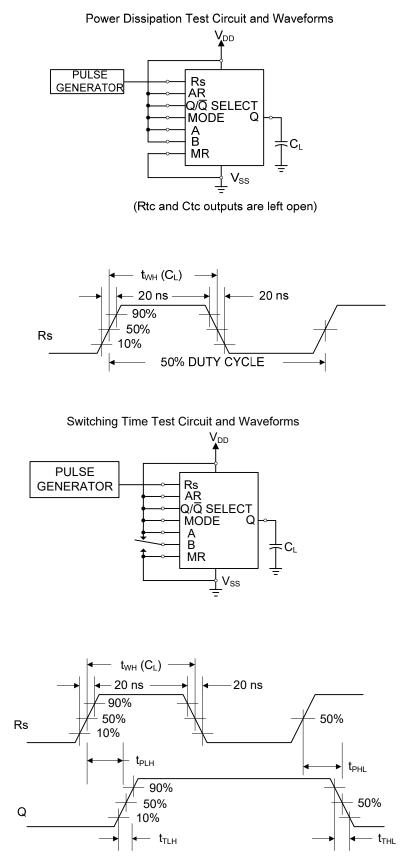

# TEST CIRCUIT AND WAVEFORMS

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.