# UNISONIC TECHNOLOGIES CO., LTD

LR2965 **CMOS IC**

# 1.5A, LOW DROPOUT REGULATOR WITH POWER **GOOD**

#### DESCRIPTION

The UTC LR2965 is CMOS-based positive voltage and a very low dropout regulator IC that minimum input voltage is 2.5V and is capable of delivering the continuous output load current up to 1.5A.

It has features of low dropout (maximum 300mV at 1A), a very low quiescent current (typically 300uA at 0.1A).

The output voltage can be set from 0.5V to (V<sub>IN</sub> - V<sub>D</sub>) with an external resistor divider and it has ±2% accuracy through all temperature ranges include the line as well as load variations. It is allowed to use a small 4.7µF MLCC input and output capacitor to deliver the current with the stable operation.

Built-in Soft-Start function reduces the inrush current and the other features are include over current protection (OCP), short-circuit protection (SCP), and thermal shut down protection (TSD).

#### **FEATURES**

- \* Input Voltage Range: 2.5V~6.0V \* Supply Current: (Typ.) 300uA

- \* Current limit: (Min.) 1.6A

- \* Adjustable Output from 0.5V

- \* LR2965: Typ 0.4V Dropout @ I<sub>OUT</sub>=1.5A

- \* Compatible with MLCC Capacitors

- \* Built-in Soft-Start Limits Inrush Current

- \* Built-in Thermal Shutdown Protection

- \* Built-in Over Current & Short Circuit Protection

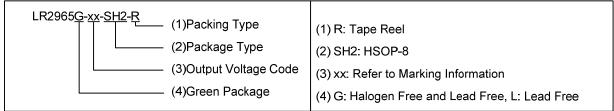

#### ORDERING INFORMATION

| Ordering Number  |                  | Dookogo | Dooking   |  |

|------------------|------------------|---------|-----------|--|

| Lead Free        | Halogen Free     | Package | Packing   |  |

| LR2965L-xx-SH2-R | LR2965G-xx-SH2-R | HSOP-8  | Tape Reel |  |

xx: Output Voltage, refer to Marking Information. Note:

www.unisonic.com.tw 1 of 5 LR2965

### MARKING INFORMATION

| PACKAGE | VOLTAGE CODE | MARKING                                                                         |  |  |

|---------|--------------|---------------------------------------------------------------------------------|--|--|

| HSOP-8  | AD: ADJ      | 8 7 6 5  UTC DDDDDate Code LR2965 L: Lead Free G: Halogen Free Lot Code 1 2 3 4 |  |  |

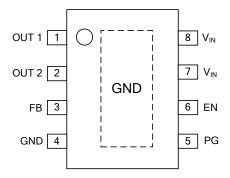

# **■ PIN CONFIGURATION**

# ■ PIN DESCRIPTION

| PIN NO.     | PIN NAME        | DESCRIPTION                                                                                                                                     |

|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2        | OUT             | Voltage Regulator Output Pin                                                                                                                    |

| 3           | FB              | Feedback Pin. Connect to output through a voltage-divider to set the output.  Recommended that the tolerance of feedback resistors is below 1%. |

| 4           | GND             | Ground Pin                                                                                                                                      |

| 5           | PG              | Open Drain Power-Good (PG) Output.                                                                                                              |

| 6           | EN              | Chip Enable Pin                                                                                                                                 |

| 7,8         | V <sub>IN</sub> | Input Supply Voltage Pin.                                                                                                                       |

| Exposed Pad | GND             | Connect exposed pad to GND.                                                                                                                     |

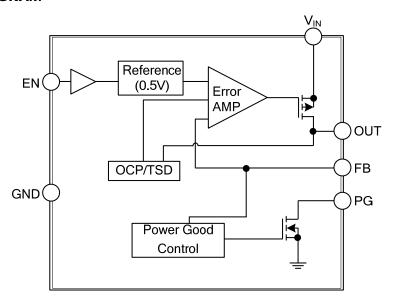

# **■ BLOCK DIAGRAM**

LR2965 cmos ic

# ■ ABSOLUTE MAXIMUM RATING (T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER            | SYMBOL           | RATINGS                  | UNIT |

|----------------------|------------------|--------------------------|------|

| Input Voltage        | $V_{IN}$         | -0.3 ~ 7                 | V    |

| Output Voltage       | OUT              | $-0.3 \sim V_{IN} + 0.3$ | V    |

| Junction Temperature | $T_J$            | +150                     | °C   |

| Storage Temperature  | T <sub>STG</sub> | -65 ~ +150               | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

### **■ RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                 | SYMBOL          | RATINGS   | UNIT |

|---------------------------|-----------------|-----------|------|

| Input Voltage Range       | V <sub>IN</sub> | 2.5 ~ 6.0 | V    |

| Ambient Temperature Range | TA              | -40 ~ +85 | °C   |

### **■ THERMAL DATA**

| PARAMETER           | SYMBOL        | RATINGS | UNIT |

|---------------------|---------------|---------|------|

| Junction to Ambient | $\theta_{JA}$ | 143     | °C/W |

| Junction to Case    | $\theta_{JC}$ | 45      | °C/W |

#### **■ ELECTRICAL CHARACTERISTICS**

All parameters are guaranteed over the operational supply voltage and temperature range. Operating conditions unless otherwise noted are:  $V_{IN}$ =5V, OUT=2.5V and  $T_A$ =25°C. Typical values are for information only.

|                                 | N 01, 00.          | 2.0 V drid TA 20 0: Typical Values are for in                            | - Cilliano |       |     |      |  |

|---------------------------------|--------------------|--------------------------------------------------------------------------|------------|-------|-----|------|--|

| PARAMETER                       | SYMBOL             | TEST CONDITIONS                                                          | MIN        | TYP   | MAX | UNIT |  |

| Supply Voltage                  |                    |                                                                          |            |       |     |      |  |

| Quiescent Current               | IQ                 | I <sub>OUT</sub> =100mA                                                  |            | 300   |     | uA   |  |

| Shutdown Current                | I <sub>STD</sub>   | V <sub>IN</sub> =6V, V <sub>EN</sub> =GND                                |            | 0.2   | 2   | uA   |  |

| Feedback (FB)                   |                    |                                                                          |            |       |     |      |  |

| Feedback Voltage Accuracy       | $V_{F}$            | I <sub>OUT</sub> =10mA, T <sub>A</sub> =25°C                             | 490        | 500   | 510 | mV   |  |

| Input Bias Current              | I <sub>F</sub>     | $V_{FB}$ =0.5V, $V_{IN}$ =6V                                             |            | 0.001 | 0.1 | uA   |  |

| Output (OUT)                    |                    |                                                                          |            |       |     |      |  |

| Output Accuracy                 | $V_{OUT}$          |                                                                          | -2         |       | 2   | %    |  |

| Load Regulation                 | $R_{LO}$           | I <sub>OUT</sub> =1mA to 1.5A                                            |            | 0.1   | 2   | %/A  |  |

| Line Regulation                 | $R_{LN}$           | V <sub>IN</sub> =2.2~6V, V <sub>OUT</sub> =1.225V, I <sub>OUT</sub> =1mA | -0.2       |       | 0.2 | %/V  |  |

|                                 |                    | I <sub>OUT</sub> =1.5A,V <sub>FB</sub> =480mV                            |            | 400   |     | mV   |  |

| Dropout Voltage                 | $V_D$              | I <sub>OUT</sub> =1A,V <sub>FB</sub> =480mV                              |            | 140   | 280 |      |  |

|                                 |                    | I <sub>OUT</sub> =0.5A,V <sub>FB</sub> =480mV                            |            |       | 200 |      |  |

| Current Limit                   | Ic                 |                                                                          | 1.6        |       |     | Α    |  |

| Load transient (Note 1)         | L <sub>OT</sub>    | I <sub>OUT</sub> =20mA to 1.5A,                                          |            | 3     |     | %    |  |

| Line Transient (Note 1)         | R <sub>NT</sub>    | ΔV <sub>IN</sub> =0.5V                                                   |            | 3     |     | %    |  |

| Enable (EN))                    |                    |                                                                          |            |       |     |      |  |

| Input Throohold                 | $V_{ENH}$          | EN rising, V <sub>IN</sub> =OUT+1V~6V                                    | 1.2        |       | 6   | V    |  |

| Input Threshold                 | $V_{ENL}$          | EN falling, V <sub>IN</sub> =OUT+1V~6V                                   |            |       | 0.4 | V    |  |

| Input Bias Current              | I <sub>EN</sub>    | EN=0 or 6V                                                               | -1         | 0     | 1   | uA   |  |

| Power Good (PG)                 |                    |                                                                          |            |       |     |      |  |

| Threehold Voltage               | P <sub>V1</sub>    | FB high, V <sub>HYS</sub> =10mV, V <sub>IN</sub> =OUT+1V~6V              |            | 550   |     | mV   |  |

| Threshold Voltage               | P <sub>V2</sub>    | FB low, V <sub>HYS</sub> =10mV, V <sub>IN</sub> =OUT+1V~6V               |            | 400   |     | mV   |  |

| Output Voltage Low              | P <sub>CL</sub>    | FB=0.4V or 0.6V, I <sub>PG</sub> =1mA                                    |            | 25    | 200 | mV   |  |

| Output Current High             | P <sub>CH</sub>    | P <sub>WRGD</sub> =6V                                                    |            | 0.001 | 0.1 | uA   |  |

| Rising Delay Time               | P <sub>RDT</sub>   | From FB*90% to PG                                                        |            | 10    |     | us   |  |

| Falling Delay Time 1            | P <sub>FDT1</sub>  | V <sub>IN</sub> =2.5V, From FB to PG                                     | 20         | 70    | 120 | us   |  |

| Falling Delay Time 2            | P <sub>FDT2</sub>  | V <sub>IN</sub> =6V, From FB to PG                                       | 60         | 180   | 300 | us   |  |

| Thermal Shutdown (TSD) (Note 1) |                    |                                                                          |            |       |     |      |  |

| TSD Threshold                   | T <sub>SDON</sub>  | TSD On                                                                   |            | 165   |     | °C   |  |

|                                 | T <sub>SDOFF</sub> | TSD Off                                                                  |            | 145   |     | °C   |  |

|                                 |                    |                                                                          |            |       |     |      |  |

Note: Guaranteed by design but not production tested.

LR2965

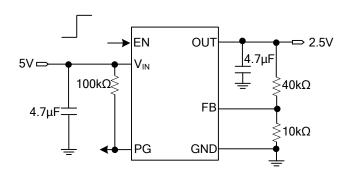

#### **■ TYPICAL APPLICATION CIRCUIT**

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.