# UNISONIC TECHNOLOGIES CO., LTD

84NXX Preliminary CMOS IC

## LOW QUIESCENT CURRENT PROGRAMMABLE-DELAY SUPERVISORY CIRCUIT

#### DESCRIPTION

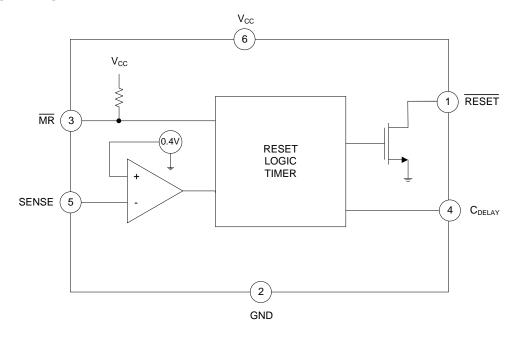

The **84NXX** can monitor and provide reset function for system voltages from 0.4V which is the microprocessor supervisory circuit. If the SENSE voltage falls below its threshold ( $V_{\text{IT}}$ ), the voltage of manual reset ( $\overline{\text{MR}}$ ) is pulled to a logic low, the  $\overline{\text{RESET}}$  signal will be asserted. The reset voltage can be factory-set from 0.9V to 5V, while the **84NXX** reset voltage is adjustable with an external resistor divider. When SENSE voltage and  $\overline{\text{MR}}$  exceed their thresholds,  $\overline{\text{RESET}}$  is driven to a logic high after a user-programmable delay time.

The **84NXX** has a very low quiescent, which makes it ideal suitable for battery-powered applications. It provides a precision reference to achieve  $\pm 1\%$  threshold accuracy. A capacitor is connected between  $C_{DELAY}$  and GND which determined reset delay time, allowing the user to select any delay time from 2.1ms to 10s. When the  $C_{DELAY}$  pin connected to  $V_{CC}$ , the delay time is selected 380ms ,while leaving the  $C_{DELAY}$  pin float, the delay time is selected 24ms.

## **■ FEATURES**

- \* Standard Voltage Rails From 0.9V to 5V and Adjustable Voltage From 0.4V are Available

- \* Low Quiescent Current: 1.6uA (typ.)

- \* Delay Time: 2.1ms to 10s

- \* High Threshold Accuracy: ±1% (typ.)

- \* Manual Reset (MR) Input

- \* Open-Drain RESET Active Low Output

- \* Immune to Short Negative SENSE voltage

- \* Guaranteed Reset Valid to V<sub>CC</sub>: 0.8V

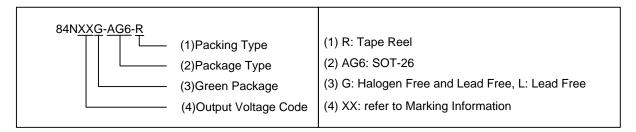

## **■** ORDERING INFORMATION

| Ordering Number |                        | Package | Packing   |  |

|-----------------|------------------------|---------|-----------|--|

| Lead Free       | Lead Free Halogen Free |         |           |  |

| 84NXXL-AG6-R    | 84NXXG-AG6-R           | SOT-26  | Tape Reel |  |

www.unisonic.com.tw 1 of 7

## MARKING INFORMATION

| PACKAGE | VOLTAGE CODE                    | MARKING                                                        |

|---------|---------------------------------|----------------------------------------------------------------|

| SOT-26  | 30: 3.0V<br>33: 3.3V<br>AD: ADJ | Voltage Code  AXX□  AXX□  L: Lead Free  G: Halogen Free  1 2 3 |

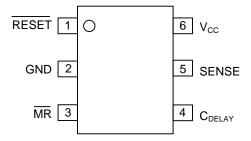

## **■ PIN CONFIGURATION**

## **■ PIN DESCRIPTION**

| PIN No. | PIN NAME           | Description                                                                          |  |  |

|---------|--------------------|--------------------------------------------------------------------------------------|--|--|

| 4       | RESET              | RESET is an open drain signal which will be asserted when the SENSE voltage drops    |  |  |

| 1       | RESET              | below a preset threshold or when the manual reset (MR) pin drops to a logic low      |  |  |

| 2       | GND                | Ground                                                                               |  |  |

| 3       | MR                 | The manual reset (MR) can introduce another logic signal to control the RESET        |  |  |

| 4       | C <sub>DELAY</sub> | Programmable reset delay time pin                                                    |  |  |

| 5       | SENSE              | SENSE pin is connected to the monitored system voltage                               |  |  |

| 6       | Vcc                | Supply voltage. A 0.1uF decoupling ceramic capacitor should be put close to this pin |  |  |

## BLOCK DIAGRAM

## ■ ABSOLUTE MAXIMUM RATINGS

| PARAMETER                  | SYMBOL              | RATINGS            | UNIT |

|----------------------------|---------------------|--------------------|------|

| Supply Voltage             | V <sub>CC</sub>     | 6.5                | V    |

| C <sub>DELAY</sub> Voltage | V <sub>CDELAY</sub> | $V_{CC} + 0.3$     | V    |

| SENSE Voltage              | V <sub>SENSE</sub>  | 6                  | V    |

| All Other Pins             |                     | 6.5                | V    |

| RESET Current              | I RESET             | 5                  | mA   |

| Power Dissipation          | P <sub>D</sub>      | 0.36               | W    |

| Junction Temperature       | TJ                  | +150               | °C   |

| Storage Temperature        | T <sub>STG</sub>    | -65 ~ <b>+</b> 150 | °C   |

Notes: 1. Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

## **■ OPERATING RANGE**

| PARAMETER             | SYMBOL          | RATINGS    | UNIT |

|-----------------------|-----------------|------------|------|

| Supply Voltage        | V <sub>IN</sub> | 1.8 ~ 6    | ٧    |

| Operating Temperature | T <sub>A</sub>  | -40 ~ +125 | °C   |

Note: The device is not guaranteed to function outside of its operating conditions.

## **■ THERMAL DATA**

| PARAMETER           | SYMBOL            | RATINGS | UNIT |

|---------------------|-------------------|---------|------|

| Junction to Ambient | $\theta_{JA}$     | 230     | °C/W |

| Junction to Case    | $\theta_{\rm JC}$ | 115     | °C/W |

<sup>2.</sup> Exceeding these ratings may damage the device.

## ■ ELECTRICAL CHARACTERISTICS

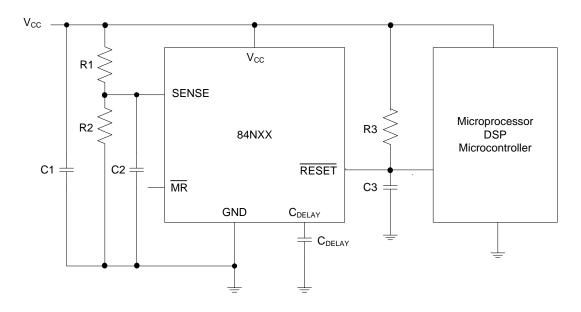

$(1.8V \le V_{CC} \le 6V, R_3 = 100k\Omega, C_3 = 47pF,$  Typical values are  $T_A = 25^{\circ}C$ , unless otherwise specified.)

| PARAMETERS                                        | SYMBOL             | CONDITIONS                                                                                                                | MIN         | TYP  | MAX                 | UNITS             |

|---------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|-------------|------|---------------------|-------------------|

| Input Supply Range                                | V <sub>CC</sub>    |                                                                                                                           | 1.8         |      | 6                   | V                 |

| Supply Current (Current late ) / Die)             | Icc                | $V_{CC}$ = 3.3V, $\overline{RESET}$ not asserted. $\overline{MR}$ , $\overline{RESET}$ , $C_{DELAY}$ open                 |             | 1.6  | 3.5                 | μA                |

| Supply Current (Current Into V <sub>CC</sub> Pin) |                    | $V_{CC}$ = 6V, $\overline{RESET}$ not asserted.<br>$\overline{MR}$ , $\overline{RESET}$ , $C_{DELAY}$ open                |             | 1.85 | 12                  | μΑ                |

| Low-level Output Voltage                          | V <sub>OL</sub>    | $1.3V \le V_{CC} < 1.8V$ , $I_{OL} = 0.4Ma$                                                                               |             |      | 0.3                 | V                 |

| Power-Up Reset Voltage (Note 1)                   |                    | $1.8V \le V_{CC} \le 6V$ , $I_{OL} = 1.0Ma$<br>$V_{OL\_MAX} = 0.2V$ , $I_{RESET} = 15Ua$<br>$T_{Rise(Vcc)} \ge 15\mu s/V$ |             |      | 0.4                 | V                 |

| Negative-going Input Threshold Accuracy           | V <sub>IT</sub>    | V <sub>SENSE</sub> falling slowly                                                                                         |             | ±1.0 | ±2.0                | %                 |

| Hysteresis on V <sub>IT</sub> Pin                 | V <sub>HYS</sub>   |                                                                                                                           |             | 1.5  | 3.5                 | V <sub>IT</sub> % |

| MR Internal Pull-up Resistance                    | RMR                |                                                                                                                           | 50          | 110  |                     | kΩ                |

| Input Current at SENSE Pin                        | I <sub>SENSE</sub> | 84NAD<br>V <sub>SENSE</sub> = V <sub>IT</sub>                                                                             | -25         |      | +25                 | nA                |

|                                                   |                    | Fixed versions, V <sub>SENSE</sub> =6V                                                                                    |             | 2.4  |                     | μΑ                |

| RESET Leakage Current                             |                    | V <sub>SENSE</sub> =6V, RESET not asserted                                                                                |             |      | 300                 | nA                |

| MR Logic Low Input                                | $V_{IL}$           |                                                                                                                           |             |      | 0.25V <sub>CC</sub> | V                 |

| MR Logic High Input                               | V <sub>IH</sub>    |                                                                                                                           | $0.7V_{CC}$ |      |                     | V                 |

| SENSE Maximum Transient Duration                  | t <sub>w</sub>     | $V_{IH} = 1.05 \ V_{IT}, \ V_{IL} = 0.95 \ V_{IT}$                                                                        |             | 17.5 |                     | μs                |

|                                                   |                    | C <sub>DELAY</sub> = Open                                                                                                 | 15          | 24   | 34                  | ms                |

| RESET Delay Time                                  | t <sub>d</sub>     | C <sub>DELAY</sub> = V <sub>CC</sub>                                                                                      | 230         | 400  | 530                 | ms                |

| RESET Delay Time                                  |                    | C <sub>DELAY</sub> = 150pF                                                                                                | 1.3         | 2.1  | 5                   | ms                |

|                                                   |                    | C <sub>DELAY</sub> = 10nF                                                                                                 | 61          | 102  | 142                 | ms                |

| MR to RESET Propagation Delay                     | t <sub>PhI1</sub>  | $V_{IH}$ = 0.7 $V_{CC}$ , $V_{IL}$ = 0.25 $V_{CC}$                                                                        |             | 160  |                     | ns                |

| High to Low Level RESET Delay, SENSE to RESET     | t <sub>Phl2</sub>  | V <sub>IH</sub> = 1.05 V <sub>IT</sub> , V <sub>IL</sub> = 0.95 V <sub>IT</sub>                                           |             | 17.5 |                     | μs                |

Note: The lowest supply voltage ( $V_{CC}$ ) at which  $\overline{\text{RESET}}$  becomes active.

## ■ STANDARD VERSIONS

| PRODUCT | NOMINAL SUPPLY VOLTAGE | THRESHOLD VOLTAGE (VIT) |

|---------|------------------------|-------------------------|

| 84N30   | 3.0V                   | 2.79V                   |

| 84N33   | 3.3V                   | 3.07V                   |

| 84NAD   | Adjustable             | 0.4V                    |

## **■ FUNCTIONAL DESCRIPTION**

#### **RESET Output Function**

The **84NXX** RESET output is typically connected to the RESET input of a microprocessor. A pull up resistor must be connected to hold this signal high, when RESET is not asserted. If the voltage is below 0.8V, RESET output is undefined. This condition can be ignored generally because that most microprocessors do not function at this state. When both SENSE and MR are higher than their threshold voltage, RESET output holds logic high. Once either of the two drops below their threshold, RESET will be asserted.

From the point that  $\overline{MR}$  is again logic high and SENSE is above  $V_{IT} + V_{HYS}$  (the threshold hysteresis),  $\overline{RESET}$  will be driven to a logic high after a reset delay time. The reset delay time is programmable by  $C_{DELAY}$  pin.

## **Monitor Multiple System Voltages**

The manual reset  $(\overline{MR})$  can introduce another logic signal to control the  $\overline{RESET}$ . When  $\overline{MR}$  is a logic low  $(0.25^*V_{CC})$ ,  $\overline{RESET}$  will be asserted. After both SENSE and  $\overline{MR}$  are above their thresholds,  $\overline{RESET}$  will be a logic high after a reset delay time. The  $\overline{MR}$  is internally connected to  $V_{CC}$  through a  $90k\Omega$  resistor so this pin can float. If the signal on  $\overline{MR}$  isn't up to  $V_{CC}$ , there will be an additional current through the  $90k\Omega$  pull up resistor. A logic-level FET can be used to minimize the leakage.

### Monitor a Voltage

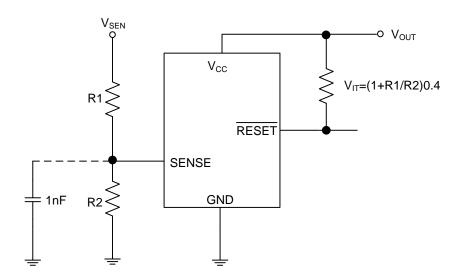

The SENSE input pin is connected to the monitored system or through a resistor network. When the voltage on the pin is below  $V_{IT}$ ,  $\overline{RESET}$  will be asserted. A threshold hysteresis will prevent the chip from responding perturbation on SENSE pin. A 1nF to 10nF bypass capacitor should be put on this pin. A typical application of the **84NXX** is shown in Figure 2. Two external resistors form a voltage divider from monitored voltage to GND. Its tap connects to the SENSE pin. The circuit can be used to monitor any voltage higher than 0.4V.

Figure 2. 84NXX MonitorIng a User- Defined Voltage

## **■ FUNCTIONAL DESCRIPTION (Cont.)**

## **Programmable Reset Delay Time**

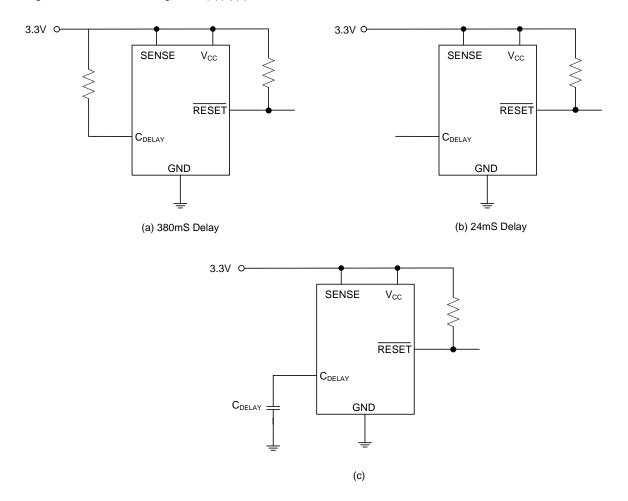

The reset delay time can be programmed by  $C_{DELAY}$  configure. When  $C_{DELAY}$  is connected to  $V_{CC}$  through a resistor between 50k  $\Omega$  and 200k $\Omega$ , the delay time is 380ms. When  $C_{DELAY}$  floated, the delay time is 24ms. A capacitor connected  $C_{DELAY}$  to GND could be used to get the user's programmable delay time from 2.1ms to 10s. The three configures can be found in Figure 3. (a)(b)(c).

Figure 3. Programmable Configurations to the Reset Delay Time

## **SENSE Voltage Transients Immunity**

The **84NXX** can be immune to SENSE pin short negative transient. The maximum immune duration is 17us while overdrive is 5%. A shorter negative transient can not assert the RESET output. The effective duration is relative to the threshold overdrive.

## ■ TYPICAL APPLICATION CIRCUIT

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.