# UNISONIC TECHNOLOGIES CO., LTD

UC3849

Advance

### LINEAR INTEGRATED CIRCUIT

### CURRENT MODE PWM CONTROLLER

#### DESCRIPTION

The UTC **UC3849** is a highly integrated low cost current mode PWM controller.

The PWM switching frequency can be programmed at normal operation externally and trimmed to tight range. The circuit works in extended 'burst mode' under no load or light load condition, which aims at minimizing switching loss. This can achieve lower standby power and higher conversion efficiency.

With a low startup current, the UTC **UC3849** could use a large value start-up resistor. Built-in slope compensation enhances the stability of the system. Leading-edge blanking on sense input removes the signal glitch due to snubber circuit diode reverse recovery.

The UTC **UC3849** includes protection function like: OCP (Cycle-by-Cycle current limiting), OLP (over load protection), UVLO (under voltage lockout). The OCP threshold compensation is internally-designed to reach constant output power. With UTC advanced frequency shuffing technique, EMI performance is greatly improved.

It has such application as laptop/power adaptor, PC/TV/set-top box power supplies, open-frame SMPS, battery charge and so on.

#### FEATURES

- \* Low  $V_{\text{IN}}/V_{\text{DD}}$  Startup Current: 3.5 $\mu\text{A}$

- \* Low Operating Current: 0.8mA

- \* Under Voltage Lockout (UVLO)

- \* Burst Mode Control for Improved Efficiency

- \* Minimum Standby Power Design

- \* Audio Noise Free Operation

- \* Programmable PWM Frequency

- \* Built-in Synchronized Slope Compensation

- \* Leading Edge Blanking on Sense Input

- \* Complete Protection Coverage with Auto Self-Recovery

- External Programmable over Temperature Protection (OTP)

- With or Without On-chip V\_DD OVP for System OVP

- Under Voltage Lockout with Hysteresis (UVLO)

- Gate Output Maximum Voltage Clamp (16V)

- Line Compensated Cycle-by-Cycle Over-Current Threshold Setting For Constant Output Current Limiting Over Universal Input Voltage Range (OCP)

- Over Load Protection. (OLP)

#### ORDERING INFORMATION

| Ordering Number                          |               | Deskers          | Decking   |  |

|------------------------------------------|---------------|------------------|-----------|--|

| Lead Free                                | Halogen Free  | Package          | Packing   |  |

| UC3849L-S08-R                            | UC3849G-S08-R | SOP-8            | Tape Reel |  |

|                                          |               |                  |           |  |

| UC3849 <u>G-S08-R</u><br>(1)Packing Type |               | (1) R: Tape Reel |           |  |

| (2)Package Type  | (2) S08: SOP-8                                  |

|------------------|-------------------------------------------------|

| (3)Green Package | (3) G: Halogen Free and Lead Free, L: Lead Free |

#### MARKING

## UC3849

Advance

#### PIN CONFIGURATION

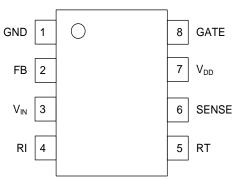

#### PIN DESCRIPTION

| PIN NO. | PIN NAME        | I/O | DESCRIPTION                                                                                                              |

|---------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------|

| 1       | GND             | Р   | Ground                                                                                                                   |

| 2       | FB              | Ι   | Feedback input pin. PWM duty cycle is determined by voltage level into this pin and current-sense signal level at Pin 6. |

| 3       | V <sub>IN</sub> | I   | Connected through a large value resistor to rectified line input for Startup IC supply and line voltage sensing.         |

| 4       | RI              | I   | Internal Oscillator frequency setting pin. A resistor connected between RI and GND sets the PWM frequency.               |

| 5       | RT              | Ι   | Temperature sensing input pin. Connected through a NTC resistor to GND.                                                  |

| 6       | SENSE           | Ι   | Current sense input pin. Connected to MOSFET current sensing resistor node.                                              |

| 7       | V <sub>DD</sub> | Р   | DC power supply pin.                                                                                                     |

| 8       | GATE            | 0   | Totem-pole gate drive output for power MOSFET.                                                                           |

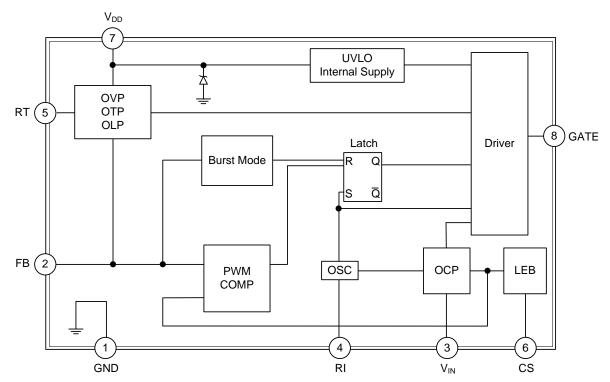

#### BLOCK DIAGRAM

#### ABSOLUTE MAXIMUM RATING

| PARAMETER                                | SYMBOL                           | RATINGS                    | UNIT |

|------------------------------------------|----------------------------------|----------------------------|------|

| DC Supply Voltage                        | V <sub>DD</sub> /V <sub>IN</sub> | 36                         | V    |

| Zener Clamp Voltage (Note 2)             | V <sub>DD</sub>                  | V <sub>DD</sub> _Clamp+0.1 | V    |

| V <sub>DD</sub> Clamp Continuous Current | I <sub>VDD</sub>                 | 10                         | mA   |

| Input Voltage                            | V <sub>FB</sub>                  | -0.3 ~ 7                   | V    |

| Input Voltage to Sense Pin               | V <sub>SENSE</sub>               | -0.3 ~ 7                   | V    |

| Input Voltage to RT Pin                  | V <sub>RT</sub>                  | -0.3 ~ 7                   | V    |

| Input Voltage to RI Pin                  | V <sub>RI</sub>                  | -0.3 ~ 7                   | V    |

| Operating Junction Temperature           | TJ                               | -20 ~ +150                 | °C   |

| Storage Temperature                      | T <sub>STG</sub>                 | -55 ~ +150                 | °C   |

Notes: 1. Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

#### THERMAL DATA

| PARAMETER           | SYMBOL          | RATINGS | UNIT |

|---------------------|-----------------|---------|------|

| Junction to Ambient | θ <sub>JA</sub> | 150     | °C/W |

#### RECOMMENDED OPERATING CONDITION

| PARAMETER                      | SYMBOL           | TEST CONDITIONS | MIN  | TYP | MAX | UNIT |

|--------------------------------|------------------|-----------------|------|-----|-----|------|

| V <sub>DD</sub> Supply Voltage | V <sub>DD</sub>  |                 | 11.5 |     | 25  | V    |

| RI Resistor Value              | RI               |                 | 100  |     | 130 | KΩ   |

| Ambient Operating Temperature  | T <sub>OPR</sub> |                 | -20  |     | 85  | °C   |

<sup>2.</sup>  $V_{DD}$  Clamp has a nominal value of 35V.

150

30

94

0.89

300

60

100

0.94

4

500

100

106

0.99

ns

ns

μA

V

mS

#### PARAMETER SYMBOL TEST CONDITION MIN TYP MAX UNIT SUPPLY SECTION Start Up Current V<sub>CC</sub>=V<sub>CCon</sub>-0.1V 4 15 IVDD(Startup) μA **Operation Current** I<sub>VDD(Operation)</sub> V<sub>FB</sub>=3V 0.8 1.8 mΑ Start Threshold Voltage 15.5 16.5 17.5 V V<sub>CC(ON)</sub> Min. Operating Voltage 8.7 9.7 11 V V<sub>CC(MIN)</sub> OVP Threshold V<sub>FB</sub>=3V V VOVP 27 28.5 30 V<sub>cc</sub> Zener Clamp Voltage V<sub>CC</sub>(clamp) I<sub>CC</sub>=10mA V 31 33 35 OSC SECTION Frequency in Normal Mode V<sub>FB</sub>=4V 60 65 70 kHz F<sub>(SW)</sub> Frequency in Power-Saving Mode $V_{FB}=1.5V$ 20 kHz Shuffling Frequency $\Delta F_{(SW)}/F_{(SW)}$ -9 +9 % Frequency Variation VS V<sub>CC</sub> % Vcc=12V ~ 25V 10 FDV Deviation Frequency Variation VS $\mathbf{F}_{\mathsf{DT}}$ T=-20 ~ 105°C 10 % Temperature Deviation DCMAX Max Duty Cycle 70 $V_{FB}=4.4V, V_{CS}=0$ 77 85 % FEEDBACK INPUT SECTION $\triangle V_{FB} / \triangle V_{CS}$ PWM Input Gain Avcs 3 V/V V<sub>FB</sub> Open Voltage V V<sub>FB(Open)</sub> 5.5 FB Pin Short Circuit Current Short FB pin to GND 0.24 mΑ IFB(Short) Burst-Mode Out FB Voltage VFB-OUT Vcs=0 1.07 V Reduce-Frequency end FB Voltage V<sub>FB-END</sub> V<sub>CS</sub>=0 V 1.13 OLP Threshold V<sub>FB-OLP</sub> Vcs=0 4.65 V Delay Time Of OLP T<sub>D-OLP</sub> mS 88 **CURRENT LIMITING SECTION** Vcs V<sub>FB</sub>=4.4V, I<sub>VIN</sub>=0 0.97 V Peak Current Limitation 0.84 1.10 L.E.B Time 350 nS Threshold Voltage For IVIN=0 V<sub>SENSE-H</sub> $I_{VIN}=0$ 0.97 V Threshold Voltage For IVIN=60uA I<sub>VIN</sub>=170uA V V<sub>SENSE-L</sub> 0.84 GATE SECTION Output Voltage Low State Vol I<sub>SINK</sub>=20mA 0.8 V V Output Voltage High State Vон I<sub>SOURCE</sub>=20mA 10

CL = 1.0 nF

CL = 1.0 nF

t<sub>R</sub>

tF

IRT

VTH(OTP)

FREQ(Shuffling)

#### ■ ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C, V<sub>DD</sub>=16V, RI=100KΩ. Unless otherwise specified)

Output Voltage Rise Time

Output Voltage Fall Time

Output Current of RT Pin

Frequency Shuffling Section

OTP Threshold Voltage

**OVER TEMPERATURE PROTECT SECTION**

FREQUENCY SHUFFLING SECTION

#### OPERATION DESCRIPTION

#### Startup Current and Start up Control

The UTC **UC3849** use a large value startup resistor which is about 2 M $\Omega$  and 1/8W, so the startup current is to be very low and power dissipation is low. For a typical AC/DC adaptor with universal input range design , a capacitor is used to provide a fast startup.

The turn-on and turn-off threshold of the UTC **UC3849** is design to 16.5V /10V. During startup, the hold-up capacitor must be charge to 16.5V through the startup resistor.

#### Frequency shuffling for EMI improvement

The UTC **UC3849** operates with the frequency shuffling/jittering (switching frequency modulation). The oscillation frequency is modulated with an internally generated random source so that the tone energy is evenly spread out. The spread spectrum minimizes the conduction band EMI, thus eases the system design in satisfying the requirement for stringent EMI.

#### **Green Power Operation**

The power dissipation of switching mode power supply is very important in zero load or light load condition, the core loss of the transformer and the loss on the snubber circuit. The transformer power loss is in proportion to the number of the switching events within a fixed period of time especially in zero load or light load condition, so reducing the switching event frequency play important part in reduction of power loss. At from no load to light/medium, when FB input above burst out threshold level (1.13V), the IC work out of burst mode. At from medium load to light load, when FB input below light load level (2.65V), the IC reduce the switching event frequency. At from light load to no load, when FB input below burst enter level (1.07V), the MOSFET transistor will be shutdown, in this way the power dissipation is reduced.

#### Current Sensing & Constant Output Power Limiting & Leading edge Blanking

The switch current is detected by a sense resistor into the sense pin. If OCP threshold voltage is fixed, output power will be change along with universal AC input range. UTC UC3489 offered Cycle-by-Cycle current limiting and OCP threshold compensation which is in aversely proportional to AC input, so that constant output power limiting can be got. When sense input is over OCP threshold voltage, the current limit comparator can turn off the external MOSFET. At initial external MOSFET on state, an internal leading edge blanking circuit turn off the sense voltage spike. The current limit comparator is disabled and thus cannot turn off the external MOSFET during the blanking period. PWM duty cycle is determined by the current sense input voltage and the FB input voltage.

#### Internal Synchronized Slope Compensation

If the IC works at CCM and duty cycle above 50%, the close loop will not stability. UTC **UC3849** adds voltage ramp onto the sense pin voltage. This greatly improves the close loop stability at CCM and prevents the sub-harmonic oscillation.

#### Gate Drive

The UTC **UC3849** Gate and the Gate of an external MOSFET are connected together for power switch control. Too weak the gate drive strength results in higher conduction and switch loss of MOSFET while too strong gate drive output compromises the EMI. Good tradeoff is achieved through the internal totem pole gate drive design with right output strength and dead time control. With this dedicated control scheme, the low idle loss and good EMI system design can be achieved easier. Moreover, an internal 16V clamp is added for MOSFET gate protection at higher than expected  $V_{DD}$  input.

#### OPERATION DESCRIPTION (Cont.)

#### **Protection Controls**

The UTC **UC3849** includes the following protection circuits for optimizing device performance and system stability: Cycle-by-Cycle current limiting (OCP), Over Load Protection (OLP), over temperature protection (OTP), on-chip  $V_{DD}$  over voltage protection (OVP) and under voltage lockout (UVLO).

Under output overload condition, the voltage at FB pin is biased higher. If FB input becomes higher than the power limit threshold value for a period of more than 88mS, control circuit would shut down the Power MOSFET. In addition, when an over temperature condition occurs, the control circuit would turn off the power MOSFET, and this device turns back to the normal operation after temperature drops below the hysteresis value.

$V_{DD}$  is supplied with transformer auxiliary winding output. It is clamped when  $V_{DD}$  exceeds 33V. When the voltage of  $V_{DD}$  pin is lower than UVLO (enter) limit, the Power MOSFET is turned off and device enters power on startup sequence thereafter.

The OCP threshold value is self adjusted lower at higher current into VIN pin. This OCP threshold slope adjustment helps to compensate the increased output power limit at higher AC voltage caused by inherent Over-Current sensing and control delay. A constant output power limit is achieved with recommended OCP compensation scheme on the UTC **UC3849**.

#### **Over Temperature Protection**

For UTC **UC3849**, in order to protect this circuit against over temperature, a NTC resistor is located between RT and GND in series with a regular. The value of this NTC transistor drops low when the ambient temperature rises. The RT pin voltage goes low at high temperature as the fixed internal current IRT flowing through the resistors. The internal OTP circuit is triggered and shutdown the MOSFET when the sensed input voltage is lower than  $V_{TH}$ \_OTP.

### UC3849

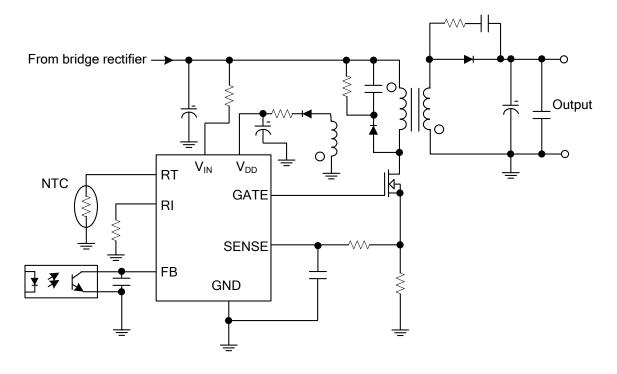

#### TYPICAL APPLICATION CIRCUIT

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.