## 4-BITS BIDIRECTIONAL MULTI-VOLTAGE LEVEL TRANSLATOR FOR OPEN-DRAIN AND PUSH-PULL APPLICATION

## DESCRIPTION

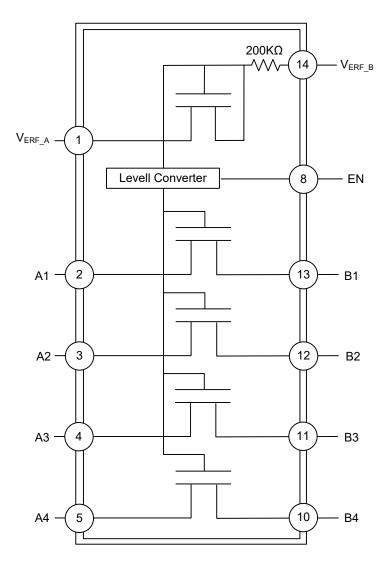

UTC **ULSF0204/D** family consists of bidirectional voltage level translators that operate from 0.8Vto 4.5V ( $V_{REF_A}$ ) and 1.8V to 5.5V ( $V_{REF_B}$ ). This range allows for bidirectional voltage translations between 0.8V and 5.0V without the need for a direction terminal in open-drain or push-pull applications. The UTC **ULSF0204/D** family supports level translation applications with transmission speeds greater than 100MHz for open-drain systems that utilize a 15-pFcapacitance and 165 $\Omega$  pull-up resistor.

When the An or Bn port is LOW, the switch is in the ON-state and a low resistance connection exists between the An and Bn ports. The low Ron of the switch allows connections to be made with minimal propagation delay and signal distortion. The voltage on the A or B side will be limited to  $V_{REF_A}$  and can be pulled up to any level between  $V_{REF_A}$  and 5V. This functionality allows a seamless translation between higher and lower voltages selected by the user without the need for directional control.

## FEATURES

- \* Provides bidirectional voltage translation with no direction pin

- \* Supports up to 100-MHz up translation and greater than 100MHz down translation at  $\leq$  30pF capacitor load and up to 40MHz up/down translation at 50pF capacitor load

- \* Supports IOFF, partial power down mode

- \* Allow bidirectional voltage level translation between

- 0.8V↔1.8/2.5/3.3/5V

- 1.2V↔1.8/2.5/3.3/5V

- 1.8V↔2.5/3.3/5V

- 2.5V↔3.3/5V

- 3.3V↔5V

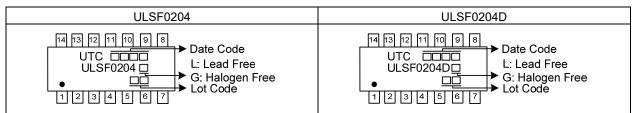

## ORDERING INFORMATION

| Ordering                          | Number                          | Daskara   | Dealing   |

|-----------------------------------|---------------------------------|-----------|-----------|

| Lead Free Halogen Free            |                                 | Package   | Packing   |

| ULSF0204L-UEB-R                   | ULSF0204L-UEB-R ULSF0204G-UEB-R |           | Tape Reel |

| ULSF0204DL-UEB-R ULSF0204DG-UEB-R |                                 | TSSOP-14U | Tape Reel |

| (1)Packing Type  | (1) R: Tape Reel                                  |  |

|------------------|---------------------------------------------------|--|

| (2)Package Type  | (2) UEB: TSSOP-14U                                |  |

| (3)Green Package | (3) G: Halogen Free and Lead Free, L: Lead Free   |  |

| (4)Logic Level   | (4) Blank: EN is high-active, D: EN is low-active |  |

|                  |                                                   |  |

### MARKING

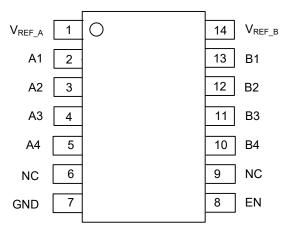

## PIN CONFIGURATION

## PIN DESCRIPTION

| PIN NO. | PIN NAME           | DESCRIPTION                                                                      |

|---------|--------------------|----------------------------------------------------------------------------------|

| 1       | $V_{REF}A$         | Reference supply voltage                                                         |

| 2~5     | An                 | Data port                                                                        |

| 6, 9    | NC                 | No connection                                                                    |

| 7       | GND                | Ground                                                                           |

| 8       | EN                 | Switch enable input<br>ULSF0204: EN is high-active ; ULSF0204D: EN is low-active |

| 10 ~ 13 | Bn                 | Data port                                                                        |

| 14      | V <sub>REF</sub> B | Reference supply voltage                                                         |

## BLOCK DIAGRAM

## FUNCTION TABLE

| PART NUMBER | INPUT EN PIN | FUNCTION |

|-------------|--------------|----------|

|             | Н            | An = Bn  |

| ULSF0204    | L            | Hi-Z     |

|             | Н            | Hi-Z     |

| ULSF0204D   | L            | An = Bn  |

Note: EN is controlled by V<sub>REF\_A</sub> logic levels.

### ■ ABSOLUTE MAXIMUM RATING (T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER                     | SYMBOL           | TEST CONDITIONS     | RATINGS    | UNIT |

|-------------------------------|------------------|---------------------|------------|------|

| Input Voltage (Note 3)        | VIN              |                     | -0.5 ~ 7   | V    |

| Input/output Voltage (Note 3) | V <sub>I/o</sub> |                     | -0.5 ~ 7   | V    |

| Continuous channel current    |                  |                     | 128        | mA   |

| Input Clamp Current           |                  | V <sub>IN</sub> <0V | -50        | mA   |

| Junction temperature          | TJ               |                     | +150       | °C   |

| Storage Temperature Range     | T <sub>STG</sub> |                     | -65 ~ +150 | °C   |

Notes: 1. Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

2. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### REOMMENDED OPRATION CONDITIONS

| PARAMETER               | SYMBOL      | TEST CONDITIONS | MIN | TYP | MAX  | UNIT |

|-------------------------|-------------|-----------------|-----|-----|------|------|

| Input/output Voltage    | Vi/o        |                 | 0   |     | 5.5  | V    |

| Reference Voltage       | VREF_A/B/EN |                 | 0   |     | 5.5  | V    |

| Pass transistor current | IPASS       |                 |     |     | 64   | mA   |

| Operating Temperature   | TA          |                 | -40 |     | +125 | °C   |

## ■ ELECTRICAL CHARACTERISTICS (T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER                                        | SYMBOL                             | TEST CC                                                                                  | TEST CONDITIONS                                                        |                            | TYP<br>(Note 1) | MAX                         | UNIT |

|--------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------|-----------------|-----------------------------|------|

| Input clamp Voltage                              | VIK                                | I <sub>I</sub> =-18mA,V <sub>EN</sub> =0                                                 |                                                                        |                            |                 | -1.2                        | V    |

| Input Leakage Current                            | I <sub>IH</sub>                    | V <sub>IN</sub> =5V,V <sub>EN</sub> =0                                                   |                                                                        |                            |                 | 5                           | μA   |

| Leakage Current from B to A                      | Icc                                | V <sub>REF_B</sub> =3.3V, V <sub>REF_A</sub><br>V <sub>I</sub> =3.3V or GND              | =V <sub>EN</sub> =1.8V, I <sub>O</sub> =0,                             |                            |                 | 3.5                         | μA   |

| Total Current through GND (Note 4)               | I <sub>CCA</sub> +I <sub>CCB</sub> | V <sub>REF_B</sub> =3.3V, V <sub>REF_A</sub><br>V <sub>I</sub> =3.3V or GND              | =V <sub>EN</sub> =1.8V, I <sub>O</sub> =0,                             |                            | 0.2             |                             | μA   |

| Control pin current                              | I <sub>IN</sub>                    | V <sub>REF_B</sub> =5.5V, V <sub>REF_A</sub><br>V <sub>EN</sub> =0 to V <sub>REF_A</sub> | =4.5V, I <sub>O</sub> =0,                                              |                            |                 | ±1                          | μA   |

| Power off Leakage current                        | I <sub>OFF</sub>                   | V <sub>REF_B</sub> = V <sub>REF_A</sub> =0, \<br>V <sub>I</sub> =5 or GND                |                                                                        |                            |                 | ±1                          | μA   |

| Input Capacitance                                | CIN                                | V <sub>I</sub> =3V or 0                                                                  |                                                                        |                            | 7.0             |                             | рF   |

| Off Capacitance                                  | $C_{IO(OFF)}$                      | $V_0=3V \text{ or } 0, V_{EN}=0$                                                         |                                                                        |                            | 5.0             | 6.0                         | pF   |

| Capacitance When Switch Is<br>Enabled            | C <sub>IO(ON)</sub>                | $V_0=3V \text{ or } 0, V_{EN}=V_{REF_A}$                                                 |                                                                        |                            | 10.5            | 13                          | pF   |

| High-Level Input Voltage for<br>EN Pin (Note 3)  | Vih                                | Vref_a=1.0V~1.5V                                                                         |                                                                        | 0.8x<br>V <sub>REF_A</sub> |                 |                             | V    |

| High-Level Input Voltage for<br>EN Pin           | VIH                                | V <sub>REF_A</sub> =1.5V~4.5V                                                            |                                                                        | 0.7x<br>V <sub>REF_A</sub> |                 |                             | V    |

| Low-Level Input Voltage for                      | VIL                                | V <sub>REF_A</sub> =1.0V~1.5V                                                            |                                                                        |                            |                 | 0.3x<br>V <sub>REF_</sub> A | V    |

| EN Pin                                           | VIL                                | V <sub>REF_A</sub> =1.5V~4.5V                                                            |                                                                        |                            |                 | 0.3x<br>V <sub>REF_A</sub>  | V    |

| Input Transition Rise or Fall<br>Rate for EN Pin | Δt/Δv                              |                                                                                          |                                                                        |                            | 10              |                             | ns/V |

|                                                  |                                    | $\lambda = 0 \lambda + -0.4m$                                                            | V <sub>REF_A</sub> =V <sub>EN</sub> =3.3V,<br>V <sub>REF_B</sub> =5V   |                            | 3               |                             | Ω    |

|                                                  |                                    | V <sub>I</sub> =0V, I <sub>O</sub> =64mA                                                 | V <sub>REF_A</sub> =V <sub>EN</sub> =1.8V,<br>V <sub>REF_B</sub> =5V   |                            | 4               |                             | Ω    |

|                                                  |                                    |                                                                                          | V <sub>REF_A</sub> =V <sub>EN</sub> =1.0V,<br>V <sub>REF_B</sub> =5V   |                            | 9               |                             | Ω    |

|                                                  |                                    | V <sub>I</sub> =0V, I <sub>O</sub> =32mA                                                 | V <sub>REF_A</sub> =V <sub>EN</sub> =1.8V,<br>V <sub>REF B</sub> =5V   |                            | 4               |                             | Ω    |

| Switch On Resistance (Note 2)                    | Ron                                |                                                                                          | V <sub>REF_A</sub> =V <sub>EN</sub> =2.5V,<br>V <sub>REF_B</sub> =5V   |                            | 10              |                             | Ω    |

|                                                  |                                    | V <sub>I</sub> =1.8V, I <sub>O</sub> =15mA                                               | V <sub>REF_A</sub> =V <sub>EN</sub> =3.3V,<br>V <sub>REF B</sub> =5V   |                            | 5               |                             | Ω    |

|                                                  |                                    | V <sub>I</sub> =1V, I <sub>O</sub> =10mA                                                 | V <sub>REF_A</sub> =V <sub>EN</sub> =1.8V,<br>V <sub>REF_B</sub> =3.3V |                            | 8               |                             | Ω    |

|                                                  |                                    | V <sub>I</sub> =0, I <sub>O</sub> =10mA                                                  | V <sub>REF_A</sub> =V <sub>EN</sub> =1.0V,<br>V <sub>REF_B</sub> =3.3V |                            | 6               |                             | Ω    |

|                                                  |                                    | V <sub>I</sub> =0, I <sub>O</sub> =10mA                                                  | V <sub>REF_A</sub> =V <sub>EN</sub> =1.0V,<br>V <sub>REF_B</sub> =1.8V |                            | 6               |                             | Ω    |

Notes: 1. All typical values are at  $T_A=25^{\circ}C$ .

2. Measured by the voltage drop between the A and B terminals at the indicated current through the switch. On-state resistance is determined by the lowest voltage of the two (A or B) terminals.

- 3. Enable pin test conditions are for the **ULSF0204**. The enable pin test conditions for **ULSF0204D** are oppositely set.

- 4. The actual supply current for **ULSF0204** is  $I_{CCA} + I_{CCB}$ , the leakage from  $V_{REF_B}$  to  $V_{REF_A}$  can be measured on  $V_{REF_A}$  and  $V_{REF_B}$  pin.

## CMOS IC

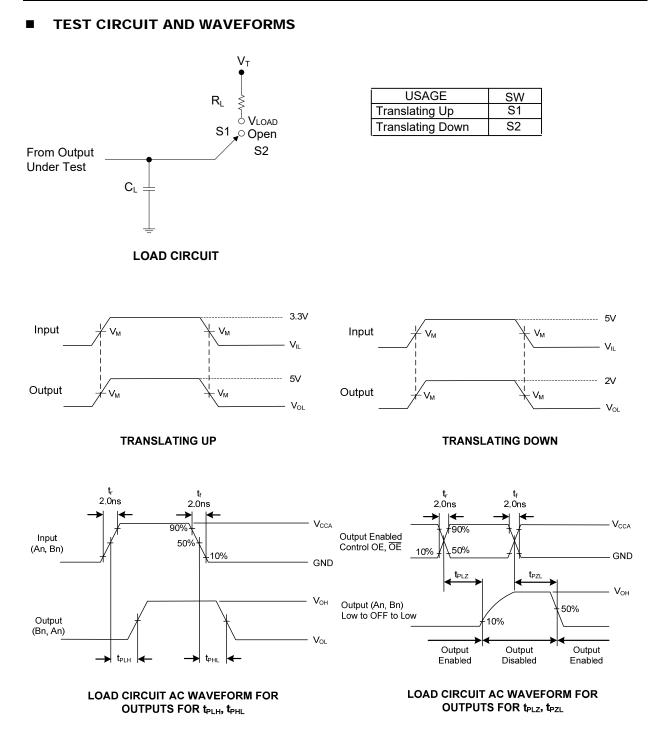

## SWITCHING CHARACTERISTICS

| PARAMETER                                 |      | SYMBOL           | TEST CONDITIONS                                                                                                          |                      |  | TYP  | MAX  | UNIT |

|-------------------------------------------|------|------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|--|------|------|------|

|                                           |      |                  | $V_{REF_A}$ =1.8V, $V_{REF_B}$ =3.3V,                                                                                    | C∟=50pF              |  | 3.8  | 5.49 | ns   |

|                                           | _    | vn               | V <sub>EN</sub> =1.8V, R <sub>L</sub> =NA, V <sub>IH</sub> =3.3V,<br>V <sub>IL</sub> =0, V <sub>M</sub> =1.15V           | C∟=15pF              |  | 1.9  | 5.19 | ns   |

|                                           | Down |                  | V <sub>REF_A</sub> =1.2V, V <sub>REF_B</sub> =3.3V,                                                                      | C∟=50pF              |  | 2.1  | 4.1  | ns   |

| Propagation Delay                         |      |                  | V <sub>EN</sub> =1.2V, R <sub>L</sub> =NA, V <sub>IH</sub> =3.3V,<br>V <sub>IL</sub> =0, V <sub>M</sub> =0.85V           | C∟=15pF              |  | 2.2  | 3.8  | ns   |

| From Input (A or B)<br>to Output (B or A) |      | t <sub>PLH</sub> | $V_{REF_A}$ =1.8V, $V_{REF_B}$ =3.3V,                                                                                    | C∟=50pF              |  | 2.3  | 5.7  | ns   |

|                                           |      |                  | V <sub>EN</sub> =1.8V, R <sub>L</sub> =500Ω,<br>V <sub>IH</sub> =1.8V, V <sub>IL</sub> =0, V <sub>M</sub> =0.9V          | C∟=15pF              |  | 1.9  | 5.13 | ns   |

|                                           | Up   |                  | $V_{REF_A}$ =1.2V, $V_{REF_B}$ =1.8V,                                                                                    | C∟=50pF              |  | 3.5  | 7.25 | ns   |

|                                           |      |                  | V <sub>EN</sub> =1.2V, R <sub>L</sub> =500Ω,<br>V <sub>IH</sub> =1.2V, V <sub>IL</sub> =0, V <sub>M</sub> =0.6V          | C∟=15pF              |  | 2.2  | 6.85 | ns   |

|                                           |      |                  | $V_{\text{REF}_A}$ =1.8V, $V_{\text{REF}_B}$ =3.3V,                                                                      | C∟=50pF              |  | 3.5  | 4.9  | ns   |

|                                           |      |                  | V <sub>EN</sub> =1.8V, R <sub>L</sub> =NA, V <sub>IH</sub> =3.3V,<br>V <sub>IL</sub> =0, V <sub>M</sub> =1.15V           | C∟=15pF              |  | 1.5  | 4.5  | ns   |

|                                           | Down |                  | $V_{REF_A}$ =1.2V, $V_{REF_B}$ =3.3V,                                                                                    | C∟=50pF              |  | 0.7  | 4.7  | ns   |

| Propagation Delay                         |      |                  | $V_{EN}$ =1.2V, RL=NA, VIH=3.3V,                                                                                         | C <sub>L</sub> =15pF |  | 0.3  | 4.3  | ns   |

| From Input (A or B)<br>to Output (B or A) |      | t <sub>PHL</sub> | V <sub>IL</sub> =0, V <sub>M</sub> =0.85V<br>V <sub>REF_A</sub> =1.8V, V <sub>REF_B</sub> =3.3V,                         | C <sub>L</sub> =50pF |  | 1.3  | 6.7  | ns   |

|                                           | Up   |                  | V <sub>EN</sub> =1.8V, R <sub>L</sub> =500Ω,<br>V <sub>IH</sub> =1.8V, V <sub>IL</sub> =0, V <sub>M</sub> =0.9V          | C <sub>L</sub> =15pF |  | 0.7  | 5.3  | ns   |

|                                           |      |                  | V <sub>REF_A</sub> =1.2V, V <sub>REF_B</sub> =1.8V,<br>V <sub>EN</sub> =1.2V, R <sub>L</sub> =500Ω,                      | C <sub>L</sub> =50pF |  | 5.5  | 7.03 | ns   |

|                                           |      |                  |                                                                                                                          | C <sub>L</sub> =15pF |  | 2.3  | 5.4  | ns   |

|                                           | Down | tPLZ             | V <sub>IH</sub> =1.2V, V <sub>IL</sub> =0, V <sub>M</sub> =0.6V<br>V <sub>REF_A</sub> =1.8V, V <sub>REF_B</sub> =3.3V,   | C <sub>L</sub> =50pF |  | 13.2 | 18   | ns   |

|                                           |      |                  | V <sub>EN</sub> =1.8V, R <sub>L</sub> =NA, V <sub>IH</sub> =3.3V,                                                        | C <sub>L</sub> =15pF |  | 9.6  | 15   | ns   |

|                                           | Up   |                  | V <sub>IL</sub> =0, V <sub>M</sub> =1.15V<br>V <sub>REF_A</sub> =1.8V, V <sub>REF_B</sub> =3.3V,                         | C∟=10pf<br>C∟=50pF   |  | 10.8 | 18   |      |

| Output Enable Time                        |      |                  | V <sub>EN</sub> =1.8V, R <sub>L</sub> =500Ω,                                                                             | · ·                  |  |      |      | ns   |

| From Input (A or B)                       | Down |                  | VIH=1.8V, VIL=0, VM=0.9V<br>VREF A=1.8V, VREF B=3.3V,                                                                    | CL=15pF              |  | 9.2  | 15   | ns   |

| to Output (B or A)                        |      |                  | V <sub>EN</sub> =1.8V, R <sub>L</sub> =NA, V <sub>IH</sub> =3.3V,                                                        | C∟=50pF              |  | 17   | 45   | ns   |

|                                           |      | t <sub>PZL</sub> | V <sub>IL</sub> =0, V <sub>M</sub> =1.15V<br>V <sub>REF_A</sub> =1.8V, V <sub>REF_B</sub> =3.3V,                         | C∟=15pF              |  | 11.7 | 37   | ns   |

|                                           | Up   |                  | $V_{EN}=1.8V, R_{L}=500\Omega,$                                                                                          | C∟=50pF              |  | 18.2 | 45   | ns   |

|                                           |      |                  | VIH=1.8V, VIL=0, VM=0.9V                                                                                                 | C∟=15pF              |  | 13.8 | 37   | ns   |

|                                           |      |                  | V <sub>REF_A</sub> =1.8V, V <sub>REF_B</sub> =3.3V,<br>V <sub>EN</sub> =1.8V, R <sub>L</sub> =NA, V <sub>IH</sub> =3.3V, | C∟=50pF              |  | 50   |      | MHz  |

|                                           | Down |                  | Vil=0, V <sub>M</sub> =1.15V                                                                                             | C∟=15pF              |  | 100  |      | MHz  |

|                                           |      |                  | V <sub>REF_A</sub> =1.2V, V <sub>REF_B</sub> =3.3V,<br>V <sub>EN</sub> =1.2V, R <sub>L</sub> =NA, V <sub>IH</sub> =3.3V, | C∟=50pF              |  | 50   |      | MHz  |

| Frequency Response<br>From Input (A or B) |      | f <sub>MAX</sub> | V <sub>IL</sub> =0, V <sub>M</sub> =0.85V                                                                                | C∟=15pF              |  | 100  |      | MHz  |

| to Output (B or A)                        |      |                  | V <sub>REF_A</sub> =1.8V, V <sub>REF_B</sub> =3.3V,<br>V <sub>EN</sub> =1.8V, R <sub>L</sub> =500Ω,                      | C∟=50pF              |  | 50   |      | MHz  |

|                                           | Up   |                  | VIH=1.8V, VIL=0, VM=0.9V                                                                                                 | C∟=15pF              |  | 100  |      | MHz  |

|                                           | ΟP   |                  | V <sub>REF_A</sub> =1.2V, V <sub>REF_B</sub> =1.8V,<br>V <sub>EN</sub> =1.2V, R <sub>L</sub> =500Ω,                      | C∟=50pF              |  | 50   |      | MHz  |

|                                           |      |                  | VIH=1.2V, KL=50002,<br>VIH=1.2V, VIL=0, VM=0.6V                                                                          | C∟=15pF              |  | 100  |      | MHz  |

Notes: 1.  $C_L$  includes probe and jig capacitance.

- 2. All input pulses are supplied by generators having the following characteristics:  $P_{RR} \le 10MHz$ ,  $Z_0 = 50\Omega$ ,  $t_r \le 2$  ns.  $t_f \le 2$  ns.

- 3. The outputs are measured one at a time, with one transition per measurement.

## DETAILED DESCRIPTION

#### Overview

The UTC **ULSF0204/D** family may be used in level translation applications for interfacing devices or systems operating at different interface voltages with one another. The UTC **ULSF0204/D** family is ideal for use in applications where an open-drain driver is connected to the data I/Os. The UTC **ULSF0204/D** can achieve 100MHz with appropriate pull-up resistors and layout. The UTC **ULSF0204/D** family can also be used in applications where a push-pull driver is connected to the data I/Os.

#### ■ FEATURE DESCRIPTION

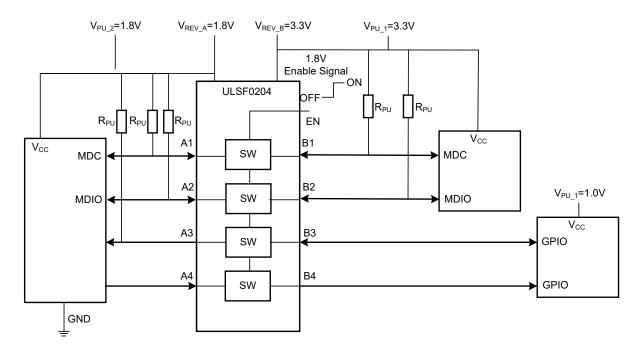

The supply voltage (V<sub>PU#</sub>) for each channel can be individually setup with a pull-up resistor. For example, CH1 can be used in up-translation mode ( $1.2V \leftrightarrow 3.3V$ ) and CH2 in down-translation mode ( $2.5V \leftrightarrow 1.8V$ ).

When EN is HIGH, the translator switch is on, and the An I/O is connected to the Bn I/O, respectively, allowing bidirectional data flow between ports. When EN is LOW, the translator switch is off, and a high-impedance state exists between ports. The EN input circuit is designed to be supplied by V<sub>REF</sub>\_A. EN must be LOW to ensure the high-impedance state during power-up or power-down.

| PART NUMBER | EN | An                            | Bn                     | DESCRIPTION                                                                   |

|-------------|----|-------------------------------|------------------------|-------------------------------------------------------------------------------|

|             | Н  | Input or output               | Input or output        | 2 state sutput mode spekle                                                    |

| ULSF0204    |    | Place all data pins in        | Place all data pins in | 3-state output mode enable<br>(active High; referenced to V <sub>REF</sub> A) |

|             | L  | 3 state mode (Hi-Z)           | 3 state mode (Hi-Z)    | (active High, referenced to VREF_A)                                           |

|             | ц  | Place all data pins in        | Place all data pins in | 2 state sutput mode spekle                                                    |

| ULSF0204D   |    | SF0204D H 3 state mode (Hi-Z) |                        | 3-state output mode enable<br>(active Low; referenced to V <sub>REF</sub> A)  |

|             | L  | Input or output               | Input or output        | (active Low, referenced to VREF_A)                                            |

Table 1. Device Comparison Table

#### APPLICATION INFORMATION

The UTC **ULSF0204/D** devices are able to perform voltage translation for open-drain or push-pull interface. Table 2 provides some consumer/telecom interfaces as reference in regards to the different channel numbers that are supported by the UTC **ULSF0204/D** family.

#### Table 2. Voltage Translator for Consumer / Telecom Interface

| Part Name  | Channel Number | Interface                                                     |

|------------|----------------|---------------------------------------------------------------|

| ULSF0204/D | 4              | GPIO, MDIO, SM Bus, PM Bus, I <sup>2</sup> C, SVIO, UART, SPI |

#### Enable, Disable, and Reference Voltage Guidelines

The **ULSF0204/D** has an EN input that is used to disable the device by setting EN LOW, which places all I/Os in the high-impedance state. Since **ULSF0204/D** is switch-type voltage translator, the power consumption is very low. It is recommended to always enable **ULSF0204/D** for bidirectional application (I<sup>2</sup>C, SMBus, PMBus, or MDIO).

|                                      |                     |                         |     |                     | 1    |

|--------------------------------------|---------------------|-------------------------|-----|---------------------|------|

| PARAMETER                            | SYMBOL              | MIN                     | TYP | MAX                 | UNIT |

| Reference Voltage (A)                | V <sub>REF</sub> _A | 0.8                     |     | 4.5                 | V    |

| Reference Voltage (B)                | V <sub>REF</sub> _B | V <sub>REF</sub> _A+0.8 |     | 5.5                 | V    |

| Input Voltage on EN Terminal(Note 1) | V <sub>I(EN)</sub>  | 0                       |     | V <sub>REF</sub> _A | V    |

| Pull-Up Supply Voltage               | V <sub>PU</sub>     | 0                       |     | $V_{REF}B$          | V    |

Notes: 1. Refer  $V_{\text{IH}}$  and  $V_{\text{IL}}$  for  $V_{\text{I(EN)}}$ .

2. Also  $V_{REF}B$  is recommended to be at 1.0V higher than  $V_{REF}A$  for best signal integrity.

3. The ULSF0204/D is able to set different voltage translation level on each channel.

4. V<sub>REF</sub>\_A must be set as lowest voltage level.

### APPLICATION INFORMATION

#### Pull-up Resistor Sizing

The pull-up resistor value needs to limit the current through the pass transistor when it is in the ON state to about 15mA. This ensures a pass voltage of 260mV to 350mV. If the current through the pass transistor is higher than 15mA, the pass voltage also is higher in the ON state. To set the current through each pass transistor at 15mA, to calculate the pull-up resistor value use the following equation:

Table 4 summarizes resistor values, reference voltages, and currents at 15mA, 10mA and 3mA. The resistor value shown in the +10% column (or a larger value) should be used to ensure that the pass voltage of the transistor is 350mV or less. The external driver must be able to sink the total current from the resistors on both sides of the UTC **ULSF0204/D** family device at 0.175V, although the 15mA applies only to current flowing through the UTC **ULSF0204/D** family device.

| V <sub>DPU</sub> | 15mA    |      | 10mA    |      | 3mA     |      |

|------------------|---------|------|---------|------|---------|------|

|                  | NOMINAL | ±10% | NOMINAL | ±10% | NOMINAL | ±10% |

| 5V               | 310     | 341  | 465     | 512  | 1550    | 1705 |

| 3.3V             | 197     | 217  | 295     | 325  | 983     | 1082 |

| 2.5V             | 143     | 158  | 215     | 237  | 717     | 788  |

| 1.8V             | 97      | 106  | 145     | 160  | 483     | 532  |

| 1.5V             | 77      | 85   | 115     | 127  | 383     | 422  |

| 1.2V             | 57      | 63   | 85      | 94   | 283     | 312  |

Table 4. Pull-up Resistor Values

#### **Family Bandwidth**

The maximum frequency of the UTC **ULSF0204/D** family is dependent on the application. The device can operate at speeds of >100 MHz gave the correct conditions. The maximum frequency is dependent upon the loading of the application. The UTC **ULSF0204/D** family behaves like a standard switch where the bandwidth of the device is dictated by the on resistance and on capacitance of the device.

The 3dB point of the UTC **ULSF0204/D** family is  $\approx$  600MHz; however, this measurement is an analog type of measurement. For digital applications the signal should not degrade up to the fifth harmonic of the digital signal. The frequency bandwidth should be at least five times the maximum digital clock rate. This component of the signal is very important in determining the overall shape of the digital signal. In the case of the UTC **ULSF0204/D** family, a digital clock frequency of greater than 100MHz can be achieved.

The UTC **ULSF0204/D** family does not provide any drive capability. Therefore higher frequency applications will require higher drive strength from the host side. No pull-up resistor is needed on the host side (3.3 V) if the UTC **ULSF0204/D** family is being driven by standard CMOS totem pole output driver. Ideally, it is best to minimize the trace length from the UTC **ULSF0204/D** family on the sink side (1.8V) to minimize signal degradation.

All fast edges have an infinite spectrum of frequency components; however, there is an inflection (or knee)in the frequency spectrum of fast edges where frequency components higher than  $f_{knee}$  are insignificant in determining the shape of the signal.

To calculate the maximum practical frequency component, or the knee frequency ( $f_{knee}$ ), use the following equations:

For signals with rise time characteristics based on 10% to 90% thresholds,  $f_{knee}$  is equal to 0.5 divided by the rise time of the signal. For signals with rise time characteristics based on 20% to 80% thresholds, which his very common in many of today's device specifications,  $f_{knee}$  is equal to 0.4 divided by the rise time of the signal.

• Keep trace length to a minimum by placing the UTC ULSF0204/D family close to the I<sup>2</sup>Coutputofthe processor.

• The trace length should be less than half the time off light to reduce ringing and line reflections or non-monotonic behavior in the switching region.

• To reduce overshoots a pull-up resistor can be added on the 1.8V side; be aware that as lower fall time is to be expected.

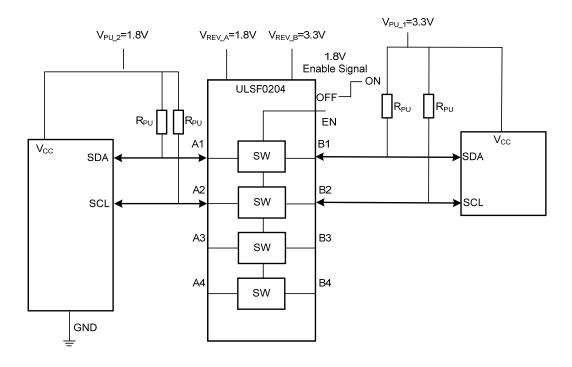

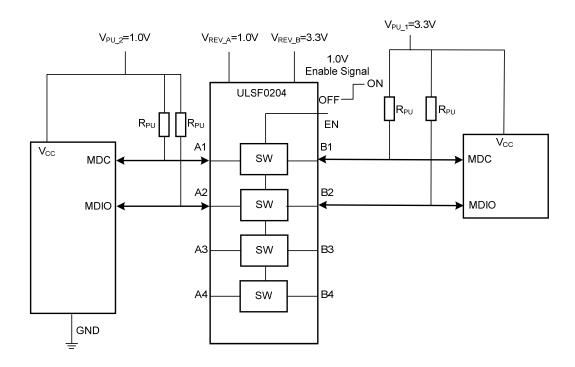

## TYPICAL APPLICATION CIRCUIT

Figure 1. Bidirectional Translation to Multiple Voltage Levels

Figure 2. Typical Application Circuit (MDIO/Bidirectional Interface)

## ■ TYPICAL APPLICATION CIRCUIT (Cont.)

Figure 3. Multiple Voltage Translation in Single Device, Application

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.