# UNISONIC TECHNOLOGIES CO.,LTD.

## F2961

## LINEAR INTEGRATED CIRCUIT

# HIGH EFFICIENT DIRECT PWM DRIVE IC

#### **DESCRIPTION**

The UTC F2961 is a high efficient, single phase and bipolar direct PWM drive motor driver IC. It is suitable for variable speed control FAN of personal computer's power supply radiation and CPU cooler with over temperature protection.

## **FEATURES**

- \* Single phase bipolar drive(16V, 1A output transistor built in.)

- \* Built in variable speed function with thermistor input signal. (External excitations direct PWM of upper side transistor control, low noise and low vibration.)

- \* Include re-circulation Diode and external parts are few.

- \* Include Hall bias circuit and thermal shut down circuit.

- \* Minimum speed settable.

- \* Full drive at open thermistor.

- \* Lock protect and auto restart function.

- \* FG output and RD output signal available.

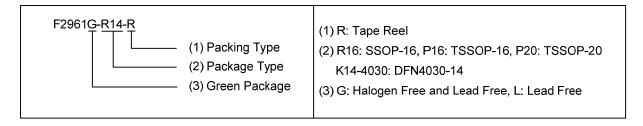

## ORDERING INFORMATION

| Ordering          | Number                    | Dookogo    | Packing   |  |

|-------------------|---------------------------|------------|-----------|--|

| Lead Free         | Halogen Free              | Package    |           |  |

| F2961L-R16-R      | F2961G-R16-R              | SSOP-16    | Tape Reel |  |

| F2961L-P16-R      | F2961G-P16-R              | TSSOP-16   | Tape Reel |  |

| F2961L-P20-R      | F2961L-P20-R F2961G-P20-R |            | Tape Reel |  |

| F2961L-K14-4030-R | F2961G-K14-4030-R         | DFN4030-14 | Tape Reel |  |

www.unisonic.com.tw 1 of 6 QW-R103-028.S

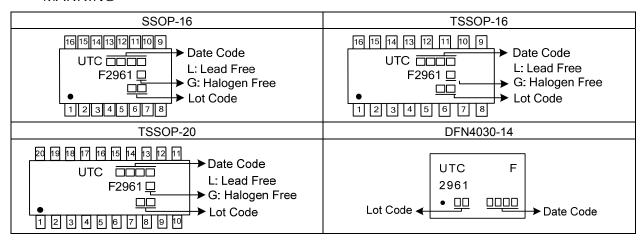

## ■ MARKING

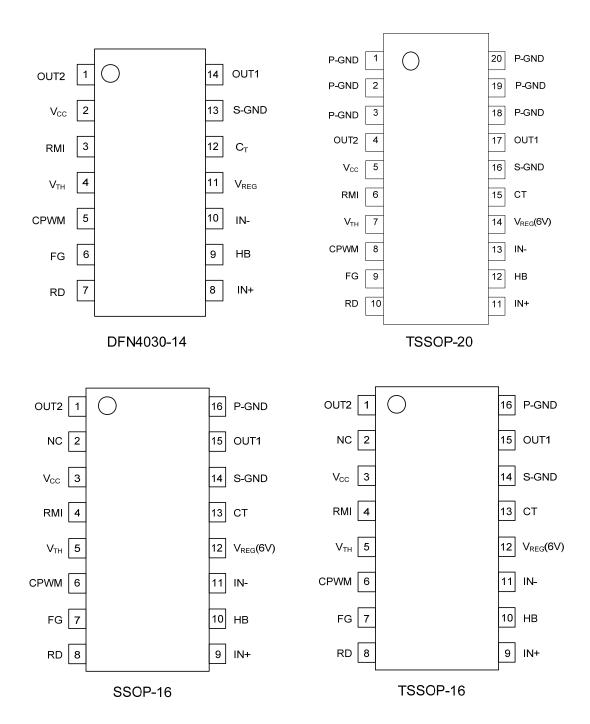

## PIN CONFIGURATIONS

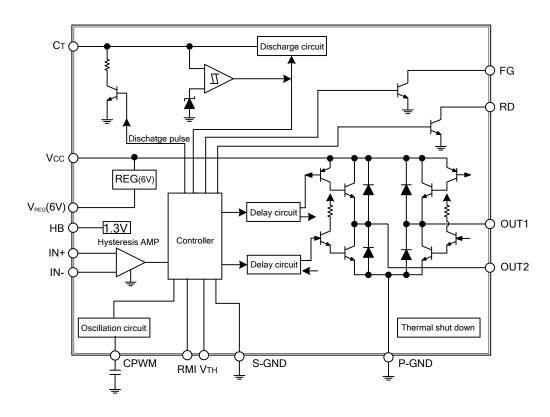

## ■ BLOCK DIAGRAM

## ■ ABSOLUTE MAXIMUM RATINGS

| PARAMETER                     | SYMBOL             | RATINGS            | UNIT |

|-------------------------------|--------------------|--------------------|------|

| Supply Voltage                | V <sub>CC</sub>    | 18                 | V    |

| Output Current                | I <sub>OUT</sub>   | 1                  | Α    |

| Output Supply Voltage         | $V_{OUT}$          | 18                 | V    |

| HB Output Current             | I <sub>HB</sub>    | 10                 | mA   |

| V <sub>TH</sub> Input Voltage | V <sub>IH</sub>    | 6                  | V    |

| RD/FG Output Supply           | $V_{RD/FG}$        | 18                 | V    |

| RD/FG Output Current          | I <sub>RD/FG</sub> | 10                 | mA   |

| Operating Temperature         | $T_{OPR}$          | -30 ~ +90          | °C   |

| Storage Temperature           | T <sub>STG</sub>   | -40 ~ <b>+</b> 150 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

## ■ THERMAL DATA

| PARAMETER           |                  | SYMBOL          | RATINGS | UNIT |

|---------------------|------------------|-----------------|---------|------|

|                     | DFN4030-14       |                 | 53      | °C/W |

| Junction to Ambient | SSOP-16/TSSOP-16 | $\theta_{JA}$   | 160     | °C/W |

|                     | TSSOP-20         |                 | 148     | °C/W |

| Junction to Case    | DFN4030-14       |                 | 10      | °C/W |

|                     | SSOP-16          |                 | 42      | °C/W |

|                     | TSSOP-16         | θ <sub>Jc</sub> | 39      | °C/W |

|                     | TSSOP-20         |                 | 35      | °C/W |

## ■ RECOMMENDED OPERATING CONDITION (T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER                             | SYMBOL           | RATINGS  | UNIT |

|---------------------------------------|------------------|----------|------|

| Supply Voltage                        | V <sub>CC</sub>  | 4.5 ~ 16 | V    |

| V Threshold Input Voltage Range       | $V_{TH}$         | 0 ~ 9    | V    |

| Common- mode Hall Input Voltage Range | V <sub>ICM</sub> | 0.2 ~ 3  | V    |

## ■ ELECTRICAL CHARACTERISTICS (V<sub>CC</sub>=12V, T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER                                     |            | SYMBOL            | TEST CONDITIONS                                     | MIN  | TYP  | MAX  | UNIT |

|-----------------------------------------------|------------|-------------------|-----------------------------------------------------|------|------|------|------|

| Operating Current Drain                       |            | I <sub>CC 1</sub> | Rotation mode                                       | 12   | 18   | 24   | mA   |

|                                               |            | I <sub>CC 2</sub> | Lock protect mode                                   | 8    | 11   | 16   | mA   |

| 6V Regulator                                  |            | $V_{REG(6V)}$     | I <sub>REG</sub> =5mA                               | 5.8  | 6    | 6.2  | V    |

| CPWM Voltage                                  | High       | $V_{CRH}$         |                                                     | 3.5  | 3.75 | 4.0  | V    |

| Crvvivi voltage                               | Low        | $V_{CRL}$         |                                                     | 1.95 | 2.0  | 2.15 | V    |

| CPWM Oscillation Frequency                    |            | FPWM              | C=100pF                                             | 18   | 25   | 32   | KHz  |

| C- nin Voltago                                | High       | V <sub>CTH</sub>  |                                                     | 3.4  | 3.6  | 3.75 | V    |

| C <sub>⊤</sub> pin Voltage                    | Low        | $V_{CTL}$         |                                                     | 1.5  | 1.6  | 1.85 | V    |

| C <sub>T</sub> Current                        | Charge     | I <sub>CT1</sub>  | V <sub>CT</sub> =1V                                 | 1.5  | 2.0  | 2.5  | μΑ   |

| C† Current                                    | Discharge  | I <sub>CT2</sub>  | V <sub>CT</sub> =4.2V                               | 0.1  | 0.2  | 0.3  | μΑ   |

| C <sub>⊤</sub> Charge/Discharge Current Ratio |            | R <sub>CT</sub>   | R <sub>CD</sub> =I <sub>CT1</sub> /I <sub>CT2</sub> | 8.5  | 10.0 | 11.5 |      |

| Lower side                                    |            | $V_{OL}$          | I <sub>OUT</sub> =200mA                             |      | 0.2  | 0.3  | V    |

| Output Saturation                             | upper side | $V_{OH}$          | I <sub>OUT</sub> =200mA                             |      | 0.9  | 1.1  | V    |

| HB Voltage                                    |            | $V_{HB}$          | I <sub>HB</sub> =5mA                                | 1.1  | 1.25 | 1.4  | V    |

| Hall input sensitivity                        |            | $V_{HN}$          | Zero to peak including offset and hysteresis        |      | 10   | 20   | mV   |

| RD/FG pin Low Voltage                         |            | $V_{FG}$          | I <sub>FG</sub> =5mA                                | •    | 0.1  | 0.3  | V    |

| RD/FG pin Leak Current                        |            | I <sub>FGL</sub>  | V <sub>FG</sub> =7V                                 |      |      | 30   | μΑ   |

## ■ TRUTH TABLE

| IN- | IN+ | CPWM | CT | OUT1 | OUT2 | FG  | RO | MODE                    |

|-----|-----|------|----|------|------|-----|----|-------------------------|

| Н   | L   |      | _  | Η    | L    | L   |    | ROTATION(DRIVE)         |

| L   | Н   | L    | L  | L    | Η    | OFF |    | PWM OFF                 |

| Н   | L   |      | _  | OFF  | L    | L   |    | ROTATION(RECIRCULATION) |

| L   | Н   | Н    | L  | L    | OFF  | OFF |    | PWM OFF                 |

| Н   | L   |      |    | Н    | OFF  | L   |    | DOCK PROTECT            |

| L   | Н   |      | Н  | OFF  | Н    | OFF |    | ROCK PROTECT            |

Note: CPWM-H = CPWM> $V_{TH}$ , CPWM-L = CPWM< $V_{TH}$

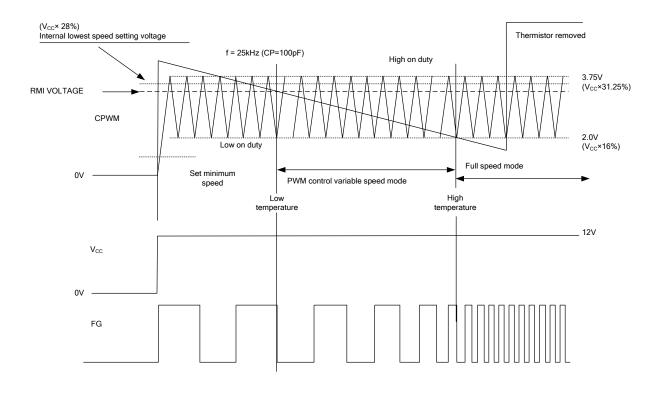

## ■ CONTROL TIMING CHART

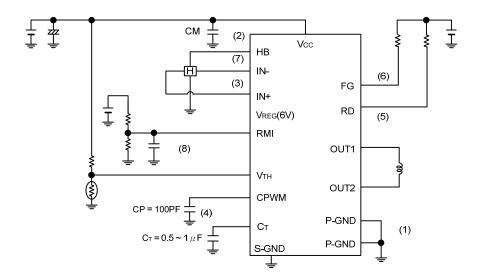

## TYPICAL APPLICATION CIRCUIT

#### (1) Voltage source-GND line layout

P-GND is connected to motor supply stage and S-GND is connected to control stage. Divides each line and external parts of control stage are connect to S-GND.

#### (2) Capacitor of re-circulation stability

CM capacitor that is for PWM drive and kick back absorption to be  $0.1 \sim 1 \mu F$  for restrain  $V_{CC}$  rising by kick back voltage. This IC is upper side transistor switching type then re-circulation current through lower side transistor. CM capacitor connects between  $V_{CC}(VM)$  and P-GND with shortest and wide line.

#### (3) Hall input

To be short lines for avoid noise. Hall input amplifier has 20mV hysteresis. Then we recommend the hall input revel to be 60mV or over.

## (4) PWM oscillation frequency setting capacitor

PWM basic frequency becomes 25 KHz when put on CP=100pF.

#### (5) RD output

Terminal is open corrector output. Low at rotation mode and High at stop mode. Open the terminal at no use.

#### (6) FG output

Output is open corrector. FG output according to rotation speed by phase change. Open the terminal at no use.

#### (7) **HB pin**

1.25V voltage reference for hall element bias.

## (8) RMI pin

The pin must be connected to  $V_{TH}$  pin if no use. Lowest speed voltage is settled 10% duty inside. If you set full speed mode when fan will start, capacitor is required.

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.