# UNISONIC TECHNOLOGIES CO., LTD

# U2525A

# LINEAR INTEGRATED CIRCUIT

# **REGULATING PWM IC**

#### ■ DESCRIPTION

The UTC **U2525A** is a pulse width modulator IC and designed for switching power supplies application to improve performance and reduce external parts usage.

A shutdown terminal controls both the soft-start circuitry and the output stages, providing instantaneous turn off through the PWM latch with pulsed shutdown, as well as soft-start recycle with longer shutdown commands. The output stage features NOR logic, giving a LOW output for an OFF state. An under-voltage lockout circuitry, which keeps the outputs off and the soft-start capacitor discharged for sub-normal input voltages, includes approximately 500 mV of hysteresis for jitter free operation. The PWM circuits also feature a latch following the comparator. When a PWM pulses has been terminated, the outputs will remain off for the duration of the period. The latch is reset with each clock pulse. The output stages are totem-pole designs capable of sourcing or sinking in excess of 200mA.

#### **■ FEATURES**

- \* Input Voltage: 8 ~ 35V

- \* On-chip +5.1V reference is trimmed to ±1%

- \* 100HZ ~ 400KHZ oscillator range

- \* Separate oscillator sync terminal

- \* Adjustable dead time control

- \* Internal soft-start

- \* Pulse-by-pulse shutdown

- \* Input under-voltage lockout with hysteresis

- \* Latching PWM to prevent multiple pulses

- \* Dual source/sink output drivers

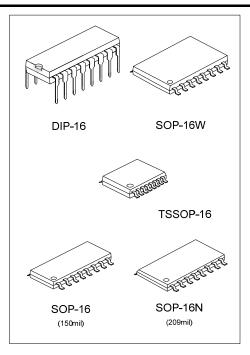

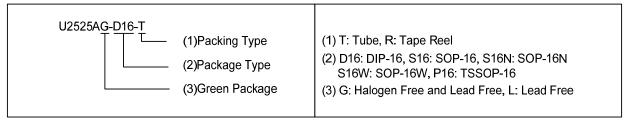

#### ORDERING INFORMATION

| Ordering       | g Number       | Dealeana | Dealine   |  |

|----------------|----------------|----------|-----------|--|

| Lead Free      | Halogen Free   | Package  | Packing   |  |

| U2525AL-D16-T  | U2525AG-D16-T  | DIP-16   | Tube      |  |

| U2525AL-S16-R  | U2525AG-S16-R  | SOP-16   | Tape Reel |  |

| U2525AL-S16N-R | U2525AG-S16N-R | SOP-16N  | Tape Reel |  |

| U2525AL-S16W-R | U2525AG-S16W-R | SOP-16W  | Tape Reel |  |

| U2525AL-P16-R  | U2525AG-P16-R  | TSSOP-16 | Tape Reel |  |

www.unisonic.com.tw 1of 10

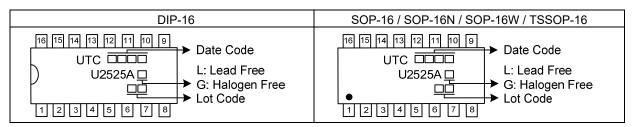

#### ■ MARKING

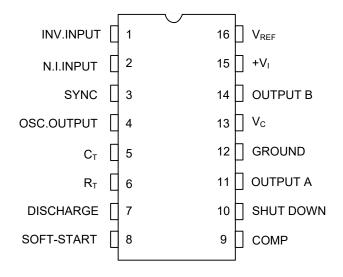

#### ■ PIN CONNECTIONS (Top View)

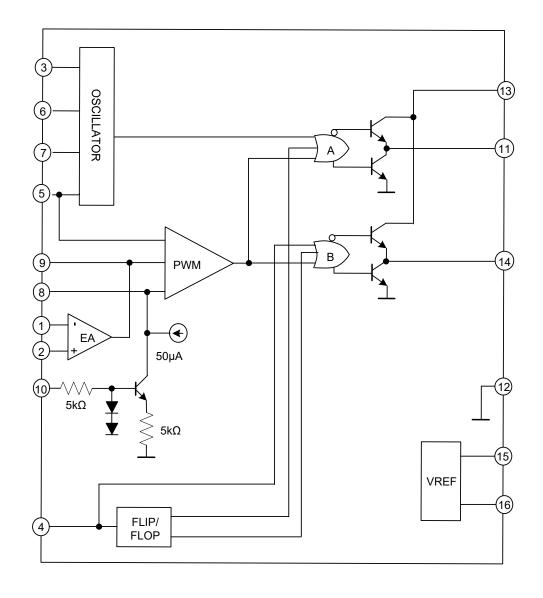

# **■ BLOCK DIAGRAM**

#### **■ ABSOLUATE MAXIUM RATINGS**

| PARAMETER                                        | SYMBOL           | RATINGS            | UNIT |

|--------------------------------------------------|------------------|--------------------|------|

| Supply Voltage                                   | $V_{iN}$         | 40                 | V    |

| Collector Supply Voltage                         | Vc               | 40                 | V    |

| Oscillator Charging Current                      | losc             | 5                  | mA   |

| Output Current, Source or Sink                   | lo               | 500                | mA   |

| Reference Output Current                         | $I_R$            | 50                 | mA   |

| Current through C <sub>T</sub> Terminal          |                  | 5                  | mA   |

| Logic Inputs                                     | Ι <sub>Τ</sub>   | - 0.3 ~ + 5.5      | V    |

| Analog Inputs                                    |                  | -0.3 ~ Vi          | V    |

| Total Power Dissipation at T <sub>A</sub> =70 °C | P <sub>D</sub>   | 1000               | mW   |

| Junction Temperature                             | TJ               | -55 ~ <b>+</b> 150 | °C   |

| Operating Ambient Temperature                    | T <sub>ORP</sub> | -40 ~ +85          | ů    |

| Storage Temperature                              | T <sub>STG</sub> | -65 ~ +150         | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

# ■ RECOMMENDED OPERATING CONDITIONS (NOTE)

| PARAMETER                               | SYMBOL            | RATINGS     | UNIT     |

|-----------------------------------------|-------------------|-------------|----------|

| Input Voltage                           | V <sub>IN</sub>   | 8 ~ 35      | <b>V</b> |

| Collector Supply Voltage                | Vc                | 4.5 ~ 35    | V        |

| Sink/Source Load Current (Steady State) | ISTEAD            | 0 ~ 100     | mA       |

| Sink/Source Load Current (Peak)         | I <sub>PEAK</sub> | 0 ~ 400     | mA       |

| Reference Load Current                  | I <sub>LOAD</sub> | 0 ~ 20      | mA       |

| Oscillator Frequency Range              | Fo                | 100 ~ 400K  | Hz       |

| Oscillator Timing Resistor              | Ro                | 2 ~ 150     | ΚΩ       |

| Oscillator Timing Capacitor             | Co                | 0.001 ~ 0.1 | μF       |

| Dead Time Resistor Range                | R⊤                | 0 ~ 500     | Ω        |

Note: Range over which the device is functional and parameter limits are guaranteed.

## **■ THERMAL DATA**

| PARAMETER           |          | SYMBOL | RATING | UNIT                                         |

|---------------------|----------|--------|--------|----------------------------------------------|

| Junction to Ambient | DIP16    | θμα    | 80     | °C/W                                         |

|                     | SOP-16   |        |        |                                              |

|                     | SOP-16W  |        | 100    | °C/W                                         |

|                     | SOP-16N  |        |        |                                              |

|                     | TSSOP-16 |        |        |                                              |

| Junction to Case    | DIP16    | θлс    | 50     | °C/W                                         |

|                     | SOP-16   |        | 60     | °C/W                                         |

|                     | SOP-16W  |        |        |                                              |

|                     | SOP-16N  |        |        | C/VV                                         |

|                     | TSSOP-16 |        |        | <u>.                                    </u> |

Note: Thermal resistance junction-alumina with the device soldered on the middle of an alumina supporting substrate measuring 15×20 mm; 0.65 mm thickness with infinite heat sink.

# ■ **ELECTRICAL CHARACTERISTICS** (V<sub>IN</sub>= 25V, T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER                                  | SYMBOL              | TEST CONDITIONS                                         | MIN    | TYP  | MAX   | UNIT    |

|--------------------------------------------|---------------------|---------------------------------------------------------|--------|------|-------|---------|

| REFERENCE SECTION                          | STIVIDUL            | TEST CONDITIONS                                         | IVIIIN | LITE | IVIAA | UNIT    |

| Output Voltage                             | V <sub>REF</sub>    | T <sub>J</sub> = 25°C                                   | 5.05   | 5.1  | 5.15  | V       |

| Total Output Variation (Note 1)            | VKEF                | Line, Load and Temperature                              | 5.00   | 3.1  | 5.2   | V       |

| Long Term Stability (Note 1)               | $\triangle V_{REF}$ | T <sub>J</sub> =125°C,1000hrs                           | 3.00   | 20   | 50    | mV      |

| Line Regulation                            | △VREF               | V <sub>IN</sub> =8 ~ 35V                                |        | 10   | 20    | mV      |

| Load Regulation                            | △VREF               | I <sub>L</sub> =0 ~ 20mA                                |        | 20   | 50    | mV      |

| Temp. Stability (Note 1)                   |                     | Over Operating Range                                    |        | 20   | 50    | mV      |

| Output Noise Voltage (Note 1)              | △ V KEF/△ I         | 10Hz ≤ f ≤ 10kHz, T <sub>J</sub> =25°C                  |        | 40   | 200   | μVrms   |

| Short Circuit Current                      |                     | V <sub>REF</sub> =0, T <sub>J</sub> =25°C               |        | 80   | 100   |         |

| OSCILLATOR SECTION                         |                     | VREF-0, 1J-25 C                                         |        | 00   | 100   | mA      |

| Clock Amplitude (Note 1, 2)                |                     |                                                         | 3      | 3.5  |       | V       |

| Sync Threshold                             |                     |                                                         | 1.2    | 2    | 2.8   | V       |

| Sync Input Current                         |                     | Sync Voltage=3.5V                                       | 1.2    | 1    | 2.5   | mA      |

| Current Mirror                             |                     | I <sub>RT</sub> =2mA                                    | 1.7    | 2    | 2.2   | mA      |

| Maximum Frequency                          | f <sub>MAX</sub>    | R <sub>T</sub> =2KΩ, C <sub>T</sub> =0.001μF            | 400    |      | 2.2   | KHz     |

| Minimum Frequency                          | f <sub>MIN</sub>    | R <sub>T</sub> =150KΩ, C <sub>T</sub> =0.1μF            | 400    |      | 100   | Hz      |

| Clock Width (Note 1, 2)                    | IMIN                | Т <sub>J</sub> =25°С                                    | 0.3    | 0.5  | 1     | μs      |

| Initial Accuracy (Note 1, 2)               |                     | T <sub>J</sub> =25°C                                    | 0.5    | ±2   | ±6    | μs<br>% |

| Voltage Stability (Note 1, 2)              |                     | V <sub>IN</sub> = 8 ~ 35 V                              |        | ±0.5 | ±1    | %       |

| Temperature Stability (Note 1)             | △f /△T              | Over Operating Range                                    |        | ±3   | ±6    | %       |

| ERROR AMPLIFIER SECTION (V <sub>CM</sub> = |                     | Over Operating Nange                                    |        | 13   | Ξ0    | /0      |

| Output Low Level                           | - 3.1 V)            |                                                         |        | 0.2  | 0.5   | V       |

| Output High Level                          |                     |                                                         | 3.8    | 5.6  | 0.5   | V       |

| Input Offset Voltage                       | Vos                 |                                                         | 0.0    | 2    | 10    | mV      |

| Input Bias Current                         | I <sub>b</sub>      |                                                         |        | 1    | 10    | μA      |

| Input Offset Current                       | I <sub>os</sub>     |                                                         |        | · ·  | 1     | μA      |

| Comm. Mode Reject.                         | CMR                 | V <sub>CM</sub> =1.5~5.2V                               | 60     | 75   |       | dB      |

| Supply Voltage Rejection                   | PSR                 | V <sub>IN</sub> =8~35V                                  | 50     | 60   |       | dB      |

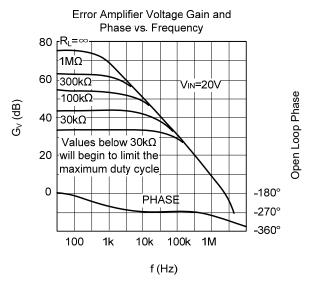

| DC Open Loop Gain                          | 1 011               | R <sub>L</sub> ≥ 10MΩ                                   | 60     | 75   |       | dB      |

| DC Transconduct. (Note 1, 3)               |                     | $30K\Omega \le R_L \le 1M\Omega, T_J = 25^{\circ}C$     | 1.1    | 1.5  |       | ms      |

| Gain Bandwidth Product (Note 1)            |                     | Gv=0dB,T <sub>J</sub> =25°C                             | 1      | 2    |       | MHz     |

| PWM COMPARATOR                             |                     | [OV 045,1] 20 0                                         |        | _    | I     |         |

|                                            |                     | Zero Duty-Cycle                                         | 0.7    | 0.9  |       | V       |

| Input Threshold (Note 2)                   |                     | Maximum Duty-Cycle                                      |        | 3.3  | 3.6   | V       |

| Input Bias Current (Note 1)                |                     | linaminani Daily Oyeis                                  |        | 0.05 | 1     | μA      |

| Minimum Duty-cycle                         |                     |                                                         |        | 0.00 | 0     | %       |

| Maximum Duty-cycle (Note 2)                |                     |                                                         | 45     | 49   |       | %       |

| SHUTDOWN SECTION                           |                     | L                                                       | 1      |      | I     |         |

| Soft Start Low Level                       |                     | V <sub>SD</sub> =2.5V                                   |        | 0.4  | 0.7   | V       |

| Shutdown Threshold                         |                     | To Outputs, V <sub>SS</sub> =5.1V, T <sub>J</sub> =25°C | 0.6    | 0.8  | 1     | V       |

| Shutdown Input Current                     |                     | V <sub>SD</sub> =2.5V                                   | 1      | 0.4  | 1     | mA      |

| Soft Start Current                         |                     | V <sub>SD</sub> =0V, V <sub>SS</sub> =0V                | 10     | 25   | 40    | μΑ      |

| Shutdown Delay (Note 1)                    |                     | V <sub>SD</sub> =2.5V, T <sub>J</sub> =25°C             |        | 0.2  | 0.5   | μs      |

# **■ ELECTRICAL CHARACTERISTICS (Cont.)**

| PARAMETER                               | SYMBOL         | TEST CONDITIONS                             | MIN | TYP | MAX | UNIT |  |

|-----------------------------------------|----------------|---------------------------------------------|-----|-----|-----|------|--|

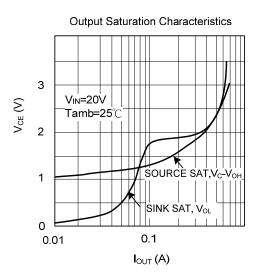

| OUTPUT DRIVERS (each output) (Vc = 20V) |                |                                             |     |     |     |      |  |

| Output Low Level                        |                | I <sub>SINK</sub> =20mA                     |     | 0.2 | 0.4 | V    |  |

|                                         |                | I <sub>SINK</sub> =100mA                    |     | 1   | 2   | V    |  |

| Output High Level                       |                | Isource=20mA                                | 18  | 19  |     | V    |  |

|                                         |                | Isource=100mA                               | 17  | 18  |     | V    |  |

| Under-Voltage Lockout                   |                | V <sub>COMP</sub> and V <sub>SS</sub> =High | 6   | 7   | 8   | V    |  |

| Collector Leakage                       | lc             | Vc=35V                                      |     |     | 200 | μΑ   |  |

| Rise Time (Note 1)                      | t <sub>R</sub> | C <sub>L</sub> =1nF, T <sub>J</sub> =25°C   |     | 100 | 600 | ns   |  |

| Fall Time (Note 1)                      | t <sub>F</sub> | C <sub>L</sub> =1nF, T <sub>J</sub> =25°C   |     | 50  | 300 | ns   |  |

| TOTAL STANDBY CURRENT                   |                |                                             |     |     |     |      |  |

| Supply Current                          | ls             | V <sub>IN</sub> =35V                        |     | 14  | 20  | mA   |  |

Notes: 1. The parameters are not 100% tested in production.

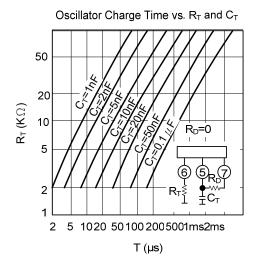

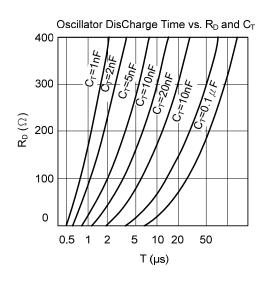

2. Tested at fosc=40 KHz (R<sub>T</sub>=3.6 K $\Omega$ , C<sub>T</sub>=10nF, R<sub>D</sub>=0  $\Omega$ ). Approximate oscillator frequency is defined by :

$$f = \frac{1}{C_{T}(0.7R_{T} + 3R_{D})}$$

3. DC transconductance  $(g_M)$  relates to DC open-loop voltage gain  $(G_V)$  according to the following equation:  $G_V = g_M R_L$  where  $R_L$  is the resistance from pin 9 to ground. The minimum  $g_M$  specification is used to calculate minimum  $G_V$  when the error amplifier output is loaded.

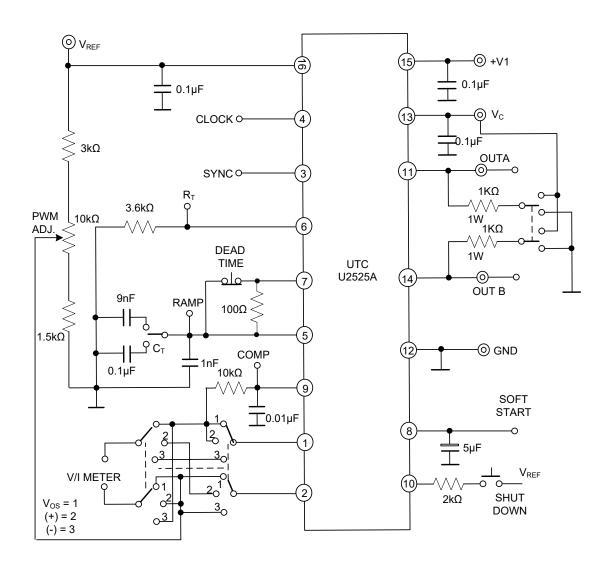

## **■ TEST CIRCUIT**

#### ■ APPLICATION INFORMATION AND CIRCUIT

#### SHUTDOWN OPTIONS (see Block Diagram)

Since both the compensation and soft-start terminals (Pins 9 and 8) have current source pull-ups, either can readily accept a pull-down signal which only has to sink a maximum of 100µA to turn off the outputs. This is subject to the added requirement of discharging whatever external capacitance may be attached to these pins.

An alternate approach is the use of the shutdown circuitry of Pin 10 which has been improved to enhance the available shutdown options. Activating this circuit by applying a positive signal on Pin 10 performs two functions: the PWM latch is immediately set providing the fastest turn-off signal to the outputs; and a 150µA current sink begins to discharge the external soft-start capacitor. If the shutdown command is short, the PWM signal is terminated without significant discharge of the soft-start capacitor, thus, allowing, for example, a convenient implementation of pulse-by-pulse current limiting. Holding Pin 10 high for a longer duration, however, will ultimately discharge this external capacitor, recycling slow turn-on upon release.

Pin 10 should not be left floating as noise pickup could conceivably interrupt normal operation.

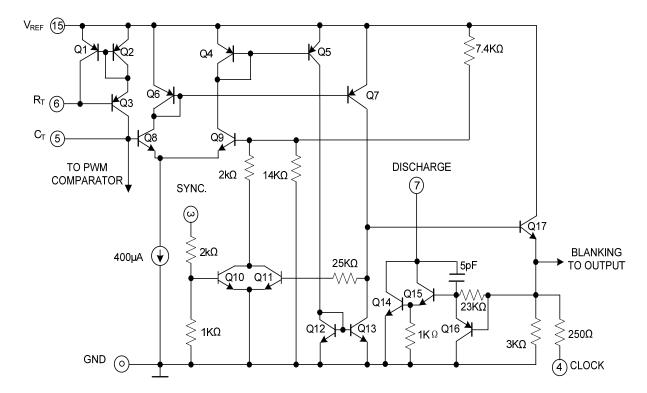

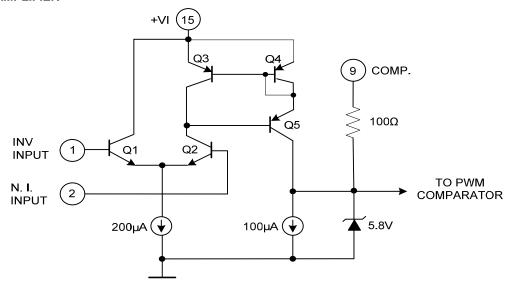

#### **OSCILLATOR SCHEMATIC**

# ■ APPLICATION INFORMATION AND CIRCUIT (Cont.)

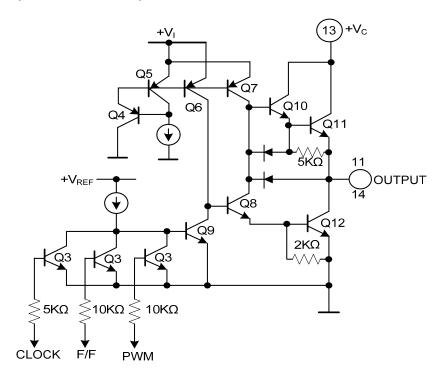

# **OUTPUT CIRCUIT (1/2 CIRCUIT SHOWN)**

## **ERROR AMPLIFIER**

#### **■ TYPICAL CHARACTERISTICS**

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.