DDR TERMINATION REGULATOR

DESCRIPTION

The UTC UR5596 is a linear bus termination regulator and

designed to meet JEDEC SSTL-2(Stub-Series Terminated Logic)

specifications for termination of DDR-SDRAM. It also can be

used in SSTL-3 or HSTL (High-Speed Transceiver Logic)

scheme. The device contains a high-speed OP AMP to provide

excellent response to the load transients, and can deliver 1.5A

continuous current and transient peaks up to 3A in the application

as required for DDR-SDRAM termination.

The UTC UR5596 also incorporates a VSENSE pin to provide

superior load regulation and a VREF output as a reference for the

chipset and DIMMs. Besides, an active low shutdown (SHDN) pin

provides Suspend To RAM (STR) functionality. When SHDN is

pulled low the VTT output will tri-state providing a high impedance

output, but, VREF will remain active. A power savings advantage

can be obtained in this mode through lower quiescent current.

Regarding the output, VTT is capable of sinking and sourcing

current while regulating the output voltage equal to VDDQ/2. The

output stage has been designed to maintain excellent load

regulation while preventing shoot through. The UTC UR5596 also

incorporates two distinct power rails that separates the analog

circuitry from the power output stage. This allows a split rail

approach to be utilized to decrease internal power dissipation and

permits UTC UR5596 to provide a termination solution for DDRII

SDRAM.

FEATURES

* Source and sink current

* Low output voltage offset

* No external resistors required

* Linear topology

* Suspend To Ram (STR) functionality

* Low external component count

* Thermal shutdown protection

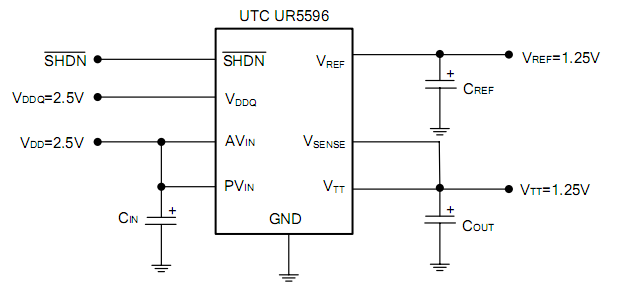

APPLICATION CIRCUIT

|