PC POWER SUPPLY SUPERVISORS

DESCRIPTION

The UTC 3511 provides protection circuits, power good output (PGO), fault protection latch (FPL_N), and protection detector function (PDON_N) control.

It can minimize external components of switching power supply systems in personal computer.

The Over Voltage Detector (OVD) monitors 3.3V, 5V, 12V input voltage level. The Under Voltage Detector (UVD) monitors 3.3V, 5V input voltage level.

When OVD or UVD detect the fault voltage level, the FPL_N is latched HIGH and PGO goes LOW. The latch can be reset by PDON_N going HIGH. There is 2.4ms delay time for PDON_N turning off FPL_N.

When OVD and UVD detect the right voltage level, the power good output (PGO) will be issue.

FEATURES

* The Over Voltage Detector (OVD) monitors 3.3V, 5V, 12V input voltage level.

* The Under Voltage Detector (UVD) monitors 3.3V, 5V input voltage level.

* Both of the power good output (PGO) and the fault protection latch (FPL_N) are Open Drain Output.

* 75 ms time delay for UVD.

* 300 ms time delay for PGO.

* 38 ms for PDON_N input signal De-bounce.

* 73 us for internal signal De-glitches.

* 2.4 ms time delay for PDON_N turn-off FPL_N.

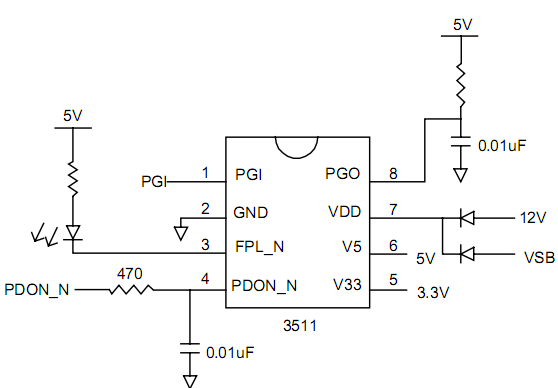

TYPICAL APPLICATION CIRCUITS

|